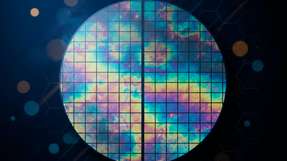

Ob Smart Homes oder Smartphones, selbstfahrende Autos oder die Industrie von morgen – all diese Zukunftstechnologien benötigen leistungsstarke Computerchips zur Steuerung. Die Systeme, die auf diesen Chips laufen, werden meist als „System on Chip (SoC)“ geschlossen entwickelt und vertrieben. Jedoch erlebt auch Open-Source-Hardware eine zunehmende Popularität. Ein Trend, der insbesondere in Zeiten der Knappheit von Computerchips als ein Schlüssel hin zur digitalen Souveränität, und damit zur Sicherung der Zukunft des Technologiestandorts Deutschland gilt.

Als Vorreiter dieser Entwicklung gilt die RISC-V-Architektur, die aufgrund ihrer Open-Source-Lizenz patentfrei zur Verfügung steht. Die offene Befehlssatz-Architektur bietet viele Vorteile: So fallen zum einen keine Patentgebühren an und zum anderen überzeugt RISC-V durch seine Standardisierung, Erweiterbarkeit und Herstellerunabhängigkeit. Die Prozessoren gelten dadurch als besonders zukunftssicher. Die Frage lautet jedoch: Wie kann schon jetzt Software für die Chips der Zukunft geschrieben werden, ohne auf die Produktion warten zu müssen?

Offene Verifikationsplattform für RISC-V-Systeme

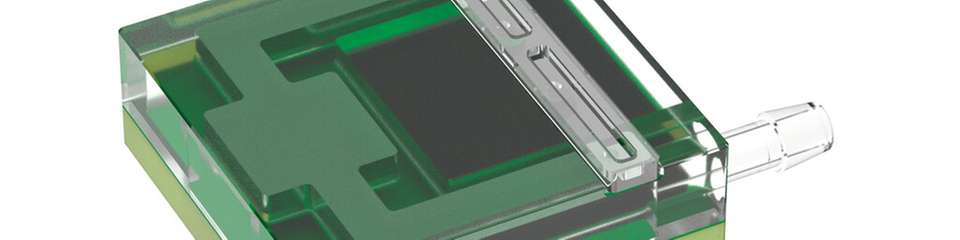

Darauf weiß Prof. Dr. Christoph Lüth vom DFKI-Forschungsbereich Cyber-Physical Systems die Antwort: „In unserem Projekt VerSys haben wir zusammen mit der Universität Bremen eine offene Verifikationsplattform für RISC-V-Systeme entwickelt, die auf einem virtuellen Prototyp für RISC-V-Systeme basiert. Virtuelle Prototypen sind eine Standardtechnik der Industrie für das Problem der frühen Softwareentwicklung. Es handelt sich dabei um einen in Form von Software entwickelten digitalen Zwilling des Chips, der mit dem echten System binärkompatibel ist und damit die Softwareentwicklung für noch nicht gefertigte Systeme erlaubt.“

Die Verifikationsplattform ist zudem skalierbar, modular und korrekt. Sie kann leicht an die Anforderungen der Nutzer angepasst werden. Ihr Quelltext ist Open Source und unter dieser URL frei verfügbar. Ende September ist das Projekt vom Wissenschaftlichen Beirat des DFKI begutachtet worden. Dieser bewertet die Ergebnisse hinsichtlich ihrer industriellen Nutzung als besonders beeindruckend und ist der Ansicht, dass die Verwertung der Ergebnisse von VerSys noch weiter zunehmen wird, je mehr Branchen sich in Folgeprojekten engagieren.

So wird beispielsweise im Projekt VE-HEP im Rahmen der Leitinitiative „Vertrauenswürdige Elektronik“ an einem gehärteten, formal verifizierten RISC-V-Prozessor geforscht, der kryptographische Operationen mit speziellen Hardwarestrukturen beschleunigen kann. Darüber hinaus wird die Plattform im Projekt ECXL weiterentwickelt, indem sie um eine RT-Ebene vergrößert wird, welche Ebenen übergreifende Verifikation und direkte Synthese des neuen Prototyps ermöglicht.

Das Projekt ECXL ist zum 1. August 2022 mit einer Laufzeit von drei Jahren gestartet und wird vom Bundesministerium für Bildung und Forschung (BMBF) mit rund 1,6 Millionen Euro gefördert.