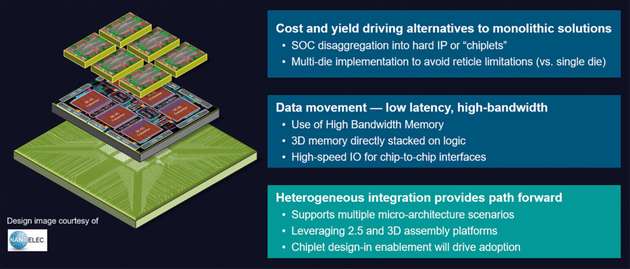

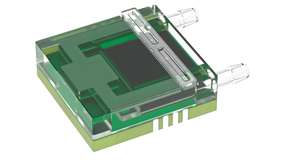

Bei diesen Packaging-Technologien wird ein normalerweise homogenes, monolithisches Bauelement wie ein ASIC oder SoC, in diskrete und ungepackte Chips zerlegt. Diese sind auch als Chiplets bekannt und wurden speziell für den Betrieb in einem Gehäuse in Verbindung mit anderen Chiplets entwickelt und optimiert. Bei diesem Workflow, der auch als heterogene Integration (HI) bezeichnet wird, werden mehrere Chips oder Chiplets in einem System-in-Package-Design (SiP) integriert.

Heterogen integrierte SiP-Bausteine bieten erhebliche Vorteile, darunter höhere Leistung, geringeren Energieverbrauch, kleinere Fläche, niedrigere Kosten und kürzere Markteinführungszeiten. Allerdings werden sie bisher nur von einer kleinen Anzahl erfahrener Anwender entworfen und hergestellt. Um sie innerhalb der Branche stärker zu verbreiten, ist eine Standardisierung der Chiplet-Modelle und IP-basierten Chip-to-Chip-Konnektivitätsmodelle erforderlich, die durch neue Workflows unterstützt werden. An dieser Aufgabe wird derzeit gearbeitet.

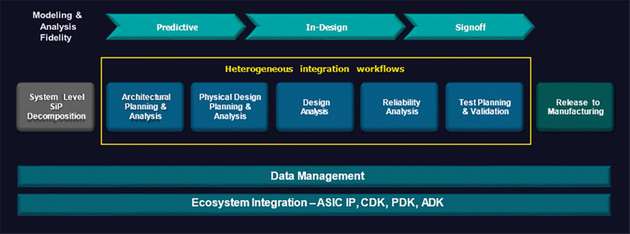

Der Artikel konzentriert sich auf fünf Workflows, die für die Planung, Implementierung, Verifizierung und das Co-Design heterogener Designs unerlässlich sind: Architekturplanung und -analyse, Physikalische Designplanung und -analyse, Designanalyse, Zuverlässigkeitsanalyse sowie Prüfplanung und Validierung. Während des Durchlaufs durch die fünf Workflows wird das Design auch einer Modellierung und Analyse unterzogen. Dabei wird kontinuierlich geprüft, ob es seine Leistungsspezifikationen erfüllt.

Prädiktive Modellierung wird während der Architekturplanungs- und der physikalischen Planungsphase angewendet. Dabei besteht das Hauptziel darin, die technischen Entscheidungen zu qualifizieren und Erkenntnisse zur nachgelagerten Leistung des Design zu gewinnen. Auf diese Weise können die Teammitglieder auch überprüfen, ob sie die richtige Packaging- und Systemarchitektur auswählen, um die Probleme, die sie zu lösen versuchen, so gut wie möglich zu behandeln.

Die In-design-Modellierung qualifiziert ein Design weiter, da während der Implementierung mehr Inhalte und Details verfügbar werden. Ziel ist es, Probleme zu identifizieren und zu beheben, solange Korrekturmaßnahmen noch relativ einfach und kostengünstig sind. Diese Probleme beziehen sich in der Regel auf Leistung, Wärme, Signalintegrität, Prozessregeln oder auch die mechanische Integration.

Signoff ist der letzte Schritt. Es ist die endgültige Abnahme des abgeschlossenen Designs vor der Freigabe für die Fertigung. Da HI-Designs ein breites Spektrum an Multi-Domain-Designinhalten und IP beinhalten, ist im Verlaufe aller fünf Workflows eine umfassende Datenmanagement-Unterstützung erforderlich. Die fünf Workflows im Detail:

Architekturplanung und -analyse

Der Workflow Architekturplanung und -analyse ermöglicht es System- und RTL-Designern, praktikable Designarchitekturen schnell zu erforschen und zu erfassen, indem sie die folgenden drei Haupterkenntnisse, die in den Prozess eingehen, ausnutzen:

Chiplet-Komponenten und zugehörige Designkits

Standard-Hochgeschwindigkeitsprotokolle für interne Chip-to-Chip-Schnittstellen im Gehäuse

Externe Chip-to-Chip-Schnittstellen zwischen dem SiP und anderen Chips innerhalb des Systems auf Leiterplattenebene

Diese Hochgeschwindigkeits-Schnittstellen können mithilfe einer Bibliothek generischer IP-Konnektivitätsmodelle erfasst und anschließend auf hersteller- und technologiespezifische Konnektivitäts-IP abgebildet werden. Hierdurch kann der Systementwickler die Strombedarfs-, Leistungs-, Flächen- und Kostenattribute verschiedener Szenarien nach Maßgabe der Systemanforderungen bewerten. Auf diese Weise hilft die prädiktive Modellierung den Designingenieuren dabei, sich durch die Identifikation einer endlichen Reihe von Szenarien, auch als Mikroarchitekturen bezeichnet, und durch die Untersuchung mehrerer Konfigurations- und Partitionsszenarien auf die optimale Mikroarchitektur zu konzentrieren.

Physikalische Designplanung und -analyse

Sobald eine optimale SiP-Architektur identifiziert ist, kann mit den Detailarbeiten begonnen werden, einschließlich der physikalischen Planung, Implementierung und Analyse. Der Workflow Physikalische Designplanung und -analyse gilt sowohl für Interposer als auch für Packaging-Substrate. Er umfasst die Package-Floor-Planung, IO-Planung, Stromversorgung, Realisierbarkeit der Substratleiterbahnen und Netzlistenoptimierung, zusammen mit den entsprechenden Prüfungen – wie LVS und LEC.

Die prädiktive Modellierung wird während der Phasen Floor-Planung und Implementierung eingesetzt, um das Design kontinuierlich zu qualifizieren, was letztlich den Designprozess optimiert. Während die Struktur des detaillierten Designs klarer wird, beispielsweise Leistungsebenen implementiert werden, verbessern sich die Modelltreue und die Qualität der Ergebnisse.

Da das Co-Design eines oder mehrerer kundenspezifischer Chiplets von grundlegender Bedeutung ist, ist es entscheidend, dass eine enge Zusammenarbeit zwischen den zuständigen Teams für das Chip- und das Packaging-Design unterstützt wird. Das bedeutet, dass eine robuste, bereichsübergreifende Verwaltung von Designdaten zusammen mit einer umfassenden Unterstützung von Änderungsaufträgen eingeführt werden muss, um den Datenaustausch zwischen Teams und Disziplinen zu erleichtern.

Designanalyse

Der Workflow Designanalyse umfasst Extraktions- und Simulationstools zur Unterstützung der Analyse der SiP-Signal- und Leistungsintegrität, des statischen und dynamischen IR-Abfalls, der Elektromigration und des Zeitverhaltens. Herkömmliche Signalintegritätstechniken können zur Simulation der Hochgeschwindigkeitsschnittstellen verwendet werden. Für Signale mit niedriger Geschwindigkeit sowie für die Prüf- und Steuerungsanschlüsse ist eine statische Analyse des Zeitverhaltens erforderlich.

Der implementierte Ansatz zur Leistungsintegrität muss zur Berücksichtigung von Multi-Chiplet-Szenarien angepasst werden. Diese Strukturen erfordern eine detaillierte parasitäre Extraktion, die sowohl Silizium- als auch organische Substrate unterstützt, sowie eine kombinierte SiP- und Chip-Extraktion für den IR-Abfall und die elektromagnetische Analyse.

Zuverlässigkeitsanalyse

Zwei Hauptbereiche, die eine umfassende Zuverlässigkeitsanalyse erfordern, sind die thermische und die mechanische Belastung. Da die Bauelemente in HI-Designs sehr nahe beieinander liegen, ist die Wahrscheinlichkeit hoch, dass es zu einer Chip-to-Chip- oder Chip-to-Package-Interaktion kommt. Daher kann die thermische Kopplung ein großes Problem darstellen. Diese intensive Ebene der Analyse erfordert detaillierte thermische Modelle der Chips. Die Modelle müssen die Leistungsdichte und die Transistorerwärmung auf Chipebene sowie die Annahme berücksichtigen, dass eine gleichmäßige Temperaturverteilung über den Chip nicht mehr realistisch ist.

Aufgrund der Größe des Substrats und der verschiedenen verwendeten Materialien kann auch die mechanische Belastung ein Problem darstellen. Beispielsweise muss die Analyse bei einem großen Silizium-Interposer mit mehreren Masken auf einem organischen Package-Substrat verschiedene Wärmeausdehnungskoeffizienten berücksichtigen und Auswirkungen wie die wärmeinduzierte Belastung an Kontakterhöhungen oder ein Verziehen des Substrats bewerten.

Das Design für die Fertigung sowie die elektrischen Regelprüfungen müssen ebenfalls auf Chiplet- und auch auf SiP-Ebene durchgeführt werden. Dazu gehören Prüfungen auf Elektromigration, elektrostatische Entladung, Latch-up und elektrische Überlastung. Zur Beschleunigung dieser Art von SiP-Analyse sollten die erforderlichen Chiplet-Modelle und Leistungsdaten in den jeweiligen Designkits enthalten sein.

Prüfplanung und Validierung

Der Fertigungstest ist vielleicht einer der anspruchvolleren Workflows bei der HI, da er eine Design-for-Test-Infrastruktur (DFT), Tests auf Waferebene, Chip-Tests innerhalb des Gehäuses und Schnittstellentests zwischen den Chips erfordert.

Eine gute Neuigkeit besteht darin, dass es etablierte DFT-Standards für die Prüfung von 2,5D- und 3D-Designs gibt, zu denen die IEEE-Standards 1838, 1687 und 1149.1 gehören. Außerdem wird dieser Workflow durch die neuesten DFT-Fortschritte unterstützt: beispielsweise durch Speichertests und integrierte Selbsttests (MBIST) mit 1838-konformen Testzugangsschnittstellen, durch Scantests, die einen 3D-Package-Muster Retargeting-Flow unterstützen, und Chip-to-Chip-Verbindungstests unter Verwendung differenzieller Verschleißablaufprozessketten, die aus Wrapper-Zellen aufgebaut sind. Wichtig ist, dass diese Methoden bereits frühzeitig in das Design einbezogen werden, um die SiP-Testung zu unterstützen; dies erfordert eine Planung auf Gehäuseebene für den Sondenzugang zu den Testpads und für die IO-Testmöglichkeiten – ähnlich den Planungsanforderungen für Hochgeschwindigkeits-IOs.

Außerdem ist es unerlässlich anzuerkennen, dass die Prüfaspekte nicht bis zum Ende des Design-Workflows warten können, sondern dass sie bereits in die Anfangsphasen der Planung einbezogen werden müssen. Die Packaging-Designingenieure müssen mit den Prüfingenieuren zusammenarbeiten, um den IO-Testplan zu entwickeln und die Anforderungen an die statische Analyse des Zeitverhaltens sowie die Anforderungen einer Zeitverhaltenssimulation zu unterstützen.

Vorteile von HI erschließen

Eine erfolgreiche Bereitstellung von Systemen mit heterogener Integration erfordert integrierte, domänenübergreifende Workflows und kollaborative Designverfahren über den gesamten Designlebenszyklus hinweg. Ein heterogenes Design erzeugt eine enorme Menge an domänenübergreifenden Daten, die den gesamten Produktlebenszyklus umfassen. Dies erfordert die Verwaltung einer Designdatenbank für das System-, RTL- und Silizium-Design und sogar für die mechanische Konstruktion. Das HI-Design umfasst auch ein breites Spektrum an IP, Materialien und Designkits. All diese Daten müssen sorgfältig verwaltet und synchronisiert werden, um während des gesamten Designprozesses Effizienz und Designintegrität zu gewährleisten.

Eine heterogene Integration hat viele Vorteile und Nutzeffekte. Sie ermöglicht größere und komplexere Systeme als monolithische SoCs und bietet verbesserte Strombedarfs-, Leistungs-, Flächen- und Formfaktoren. Doch diese Vorteile lassen sich nicht gratis erzielen. Dabei sind einige Herausforderungen zu bewältigen. Dazu gehören eine optimale Schaltungsaufteilung und Architekturauswahl, eine effiziente Stromversorgung im gesamten System sowie die Gesichtspunkte Wärmemanagement, Zeitverhalten und Prüfung. Unternehmen, die diese Herausforderungen meistern und die Vorteile des HI-Designs voll ausschöpfen möchten, sollten ihre Bemühungen auf die Entwicklung, Qualifizierung und Bereitstellung der fünf in diesem Artikel vorgestellten Workflows konzentrieren.