Was soll ein Computerchip leisten? Welche Architektur soll er haben und welche Komponenten beinhalten? Wie soll der Schaltplan aussehen, wo sollen Verbindungen und Transistoren platziert werden? Solche Fragen werden im Chipdesign beantwortet. Geeignete Designwerkzeuge und -Bibliotheken sind hier entscheidend für die Realisierung von anwendungsspezifischen integrierten Schaltkreisen mit hoher Performance, Zuverlässigkeit und Hardwaresicherheit.

Im Projekt „DI-ReDesign“ arbeiten Globalfoundries (Dresden), NaMLab (Dresden), die Ruhr-Universität Bochum, die Universität Bremen, die Technische Universität Berlin, die Technische Hochschule Mittelhessen (Gießen) und das Fraunhofer IMWS zusammen, um Open-Source-Designtools und Logikbibliotheken zu entwickeln, die speziell auf neuartige rekonfigurierbare Transistoren (RFETs) zugeschnitten sind. „Diese Halbleiterbauelemente ermöglichen eine höhere Integrationsdichte, verbesserte Energieeffizienz und schnellere Schaltgeschwindigkeiten. Auch für Cybersicherheit, Temperaturstabilität und Signalqualität bieten RFETs erhebliche Vorteile, was sie für eine Vielzahl von Anwendungen interessant macht“, sagt Frank Altmann, Leiter des Geschäftsfelds „Werkstoffe und Bauelemente der Elektronik“, der das Projekt am Fraunhofer IMWS koordiniert.

Offene Designbibliotheken für RFET-basierte Schaltungen

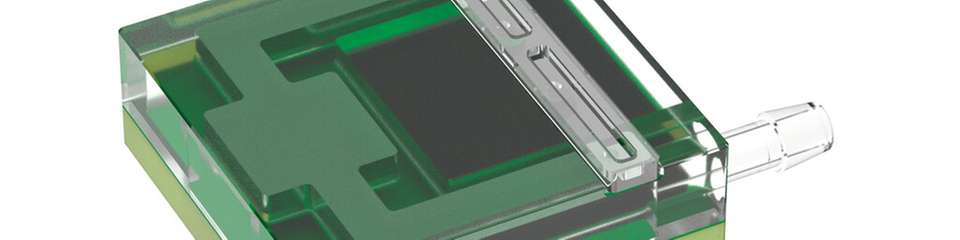

Die einzigartigen Eigenschaften von RFETs erlauben vielseitige Anwendungen in digitalen und analogen Schaltungen, etwa für Signalverarbeitung, neuronale Netze und Niedertemperatur-Elektronik. Um dafür komplexe, hochinnovative Schaltungsdesigns umsetzen zu können, sollen eine offene Designbibliothek und eine automatisierte Design-Umgebung (Electronic Design Automation, EDA) entstehen. Damit wollen die Projektpartner eine Open-Source-Entwicklungsumgebung für neuartige Elektroniklösungen auf Basis von RFETs bereitstellen. Die Bibliothek beinhaltet dabei Kerneigenschaften der Zellen für logische und physikalische Synthese, ohne Informationen über den genauen Prozess oder die zugrundeliegende Bauteilphysik preiszugeben.

„Die Industrie kann dann sehr schnell auf den neuen Design-Tools aufbauen, diese adaptieren und erweitern. Das erleichtert den Zugang zur RFET-Technologie und verbessert das Chipdesign auch im Hinblick auf die Hardware-Sicherheit“, sagt Altmann. Die Designer und Endkunden erhalten darüber hinaus durch die Projektergebnisse auch die Möglichkeit, bei der Entwicklung ihrer Produkte die Widerstandsfähigkeit gegen mögliche Angriffsszenarien frühzeitig mit einzubeziehen.

Sicherheitsprüfung von Chips gegen Hardware-Angriffe

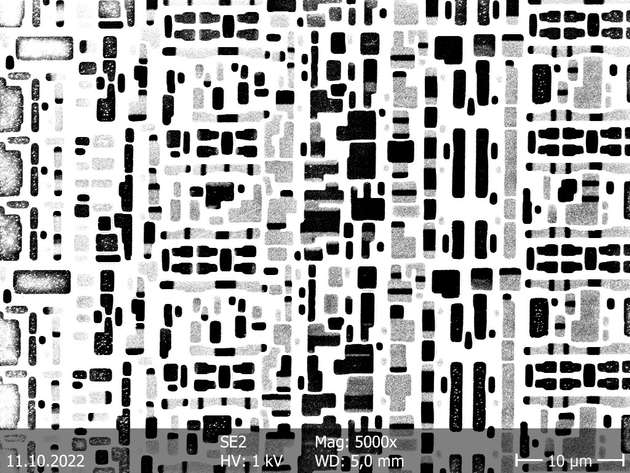

Die Aktivitäten des Fraunhofer IMWS im Projekt zielen dabei vor allem darauf ab, diese Resilienz der Schaltungen gegenüber Reverse Engineering und Manipulation zu prüfen. Potenzielle Angreifer versuchen mit speziellen Seitenkanal-Methoden, logische Verschaltungen der Chipstrukturen oder elektrische Signalverläufe herauszufinden, Schaltvorgänge und Speicherinhalte auszulesen oder zu beeinflussen. Dies ermöglicht Fälschungen, Beeinflussung der Chip-Funktionalität oder Missbrauch sensibler Informationen. Die in „DI-ReDesign“ entworfenen Schaltungsblöcke werden deshalb umfassend auf ihre Sicherheit gegenüber Hardware-Angriffen bewertet. Erkannte Schwachstellen können dann direkt durch ein angepasstes Chipdesign berücksichtigt werden.

Das Fraunhofer IMWS setzt dabei hochauflösende elektronenmikroskopische Abtastverfahren ein, sogenanntes e-beam Probing, um potenzielle Angriffsszenarien zu prüfen. „Wir können beispielsweise die Beschaltung der RFETs über rasterelektronenmikroskopische Kontrastmechanismen direkt visualisieren und sogar durch die Interaktion mit dem Elektronenstrahl beeinflussen. Zudem entwickeln wir von uns bereits erprobte Präparationstechniken weiter, um die Machbarkeit und Effizienz für den großflächigen Zugang zu Transistorstrukturen zu evaluieren“, sagt Altmann. Auch neue Verfahren zur Signalverfolgung kommen dabei zum Einsatz und werden auf ihr Gefahrenpotenzial für Hardware-Attacken überprüft.