Konventionelle Wandler für Militär und Industrie nutzen häufig Silizium-IGBTs. Netzgebundene erneuerbare Energien, Energiespeicher oder unterbrechungsfreie Stromversorgungen sind Beispiele für Rund-um-die-Uhr-Anwendungen, bei denen ein Wechsel von der Silizium- (Si) zur Siliziumkarbid-Technologie (SiC) einen hohen Nettokapitalwert über den Lebenszyklus, hohe Rentabilität oder kürzere Amortisationszeiten bringt. Diese Vorteile ergeben sich allerdings nicht aus dem Vergleich der kalkulierten Stücklistenkomponenten, sondern bei der Betrachtung des SiC-

Systemwertversprechens. Dieses Ver-

sprechen sollte folglich die Wertschöpfungskette sowohl für Si- als auch für SiC-Designs detailliert bewerten. Im Folgenden wird erörtert, wie ein SiC-basierter Dreiphasen-Zweistufen-Wechselrichter mit einem Gewicht von 16 kg auf Systemebene mit einem Subsystem-Designansatz optimiert wurde. Dieser sollte die SiC-Vorteile hinsichtlich Leistungsdichte, Effizienz, Leistungsmodulauslastung und hoher Betriebstemperatur erhöhen. Der Fokus liegt auf der Optimierungsphase des Leistungsmoduls, der Zwischenkreiskondensatoren und der DC-Busstruktur.

Um die Systemeffizienz und Leistungsdichte SiC-basierter Wandlersysteme zu optimieren, müssen zunächst Designkompromisse bei verschiedenen Komponenten und Subsystemen ermittelt und priorisiert werden. Anschließend müssen aufgrund der inhärenten Kopplung die elektrischen, mechanischen und thermischen Wechselwirkungen sorgfältig berücksichtigt werden. Auf jedes Subsystem wird eine proprietäre CAD-basierte Optimierungsmethode angewendet, wobei Eingänge, Ausgänge und Mehrbereichsphysik an der Schnittstelle bekannt sein müssen. Dank dieses Optimierungsansatzes kann der Endanwender die Extrempunkte des Lösungsraumes abdecken, um die Vorteile SiC-basierter Systeme zu maximieren.

Das Leistungsmodul im Detail

Das Leistungsmodul CAS325M12HM2 von Wolfspeed wurde für militärische, industrielle und automobile Motorantriebsanwendungen entwickelt, um die Vorteile SiC-basierter Halbleiterbauelemente zu nutzen. Das reine SiC-Leistungsmodul bietet 1.200 V, 445 A

und 3,6 mΩ On-Widerstand (7-×-

25-mΩ-MOSFETs und 6-×-50-A-Schottky-Dioden pro Schalterstellung) und arbeitet bei einer Höchsttemperatur von 175 °C. Das Halbbrückenleistungsmodul CAS325M12HM2 weist einen Leistungspfad mit niedriger parasitärer Induktivität (Lσ ~ 5,5 nH bei 1 MHz) und symmetrische Signalpfade mit niedriger Induktivität auf. Hierdurch kann das Leistungsmodul erforderlichenfalls bei über 150 kHz schalten.

Die Kommutationsschleife, die den laminierten DC-Bus und die Zwischenkreiskondensatorbank umfasst, muss eine Struktur mit minimalem ESL aufweisen. Daher wird eine Comsol-Multiphysics-Modellierung des laminierten Sammelschienendesigns genutzt, um die hochfrequenten elektrischen Strompfade zu eruieren, die Auswirkungen von Skin- und Proximity-Effekten zu quantifizieren und die äquivalente Induktivität der CAS325M12HM2-Leistungsanschlüsse zu bestimmen. Die Zwischenkreisspannung des Wechselrichters wird durch die Spannungsüberhöhung infolge der in der parasitären Induktivität gespeicherten Energie eingeschränkt, von der die Drain- und Source-Anschlüsse des Leistungsmoduls während der Abschaltung betroffen sind. Diese parasitäre Induktivität Lσ kombiniert mit höheren di/dt-Werten beeinflusst die Spannung und die Stromnutzung des Leistungsmoduls auf zweierlei Art negativ. Zum einen kommt die Spannungsüberhöhung ΔVovershoot = - Lσ (di/dt) zur Zwischenkreisspannung hinzu. Dies zwingt Vbus zu einem künstlich niedrigen Wert, da Vbus + Δv0-peak + Vovershoot + Sicherheitsmarge strikt unter dem Modulrating liegen müssen. Hier ist Δv0 peak die höchste Gleichspannungswelligkeit infolge der Interaktion des AC-Stroms mit dem ESR der Kondensatorbank.

Zweitens muss der Modulstrom auch während der Abschaltung eingeschränkt oder verlangsamt werden, um den di/dt-Wert und damit die Spannungsüberhöhung zu begrenzen. Die Verlangsamung des Bauelementes während der Abschaltung hat zusätzliche Schaltverluste zur Folge, die das Bauelement thermisch beeinträchtigen und die Gesamteffizienz des Systems benachteiligen. Die Reduzierung des di/dt-Werts durch Begrenzung des Stroms oder durch verringerte Flankensteilheit beim Abschaltverhalten, führt zwangsläufig dazu, die eigentlichen SiC-Modul-Vorteile nur unvollständig auszunutzen. Daher sollte man die parasitäre Induktivität der laminierten DC-Busstruktur minimieren.

Optimierung von innen heraus

Bei der Maximierung der Systemleistung durch SiC-Halbleiterbauelemente ist es wichtig, das System „von innen heraus“ zu optimieren, also vom SiC-Chip in jeder Leistungsmodulschalterstellung über die Außenseiten des Leistungsmoduls bis hin zu allen angebundenen Subsystemen. Das DC-Bussing ist ein multiphysikalisches Designproblem im elektrischen, thermischen und mechanischen Bereich.

In enger Zusammenarbeit mit einem Anbieter laminierter Stromschienen hat Wolfspeed eine Konfiguration mit ex-

trem niedriger DC-Bus-Induktivität für einen reinen SiC-Wechselrichter mit 250 kW bei 1.200 V entwickelt. In dieser Designiteration sollte eine maximierte Magnetfeldunterdrückung gewährleistet und die parasitäre Induktivität des Bussing-Systems reduziert werden, von der das Leistungsmodul betroffen ist. An der laminierten DC-Busstruktur erfolgte eine elektrische Modellierung und FEA-Analyse ohne Zwischenkreiskondensatoren, um die Kommutationsschleife zu minimieren und den hohen di/dt-Wert zu stützen, der während der Kommutationsintervalle des Leistungsmoduls erforderlich war. Die laminierte DC-Busstruktur wurde im CAD-Tool modifiziert.

Es wurden sechs Cu-Bänder hinzugefügt, um die laminierten DC-Bus-V+- und -V--Flächen zu kürzen; diese waren notwendig, um alle von den Leistungsanschlüssen der drei Module ausgehenden hochfrequenten elektrischen Strompfade zu „schließen“. Zudem haben die sechs Cu-Verbindungen zwischen den laminierten V+- und V--Flächen und den Leistungsanschlüssen der drei Module DC+ beziehungsweise DC‑ eine besondere Form: Es wurde ein solider Cu-Stab verwendet, der für die Leitungen des Leistungsmoduls CAS325M12HM2 optimiert war. Die Stabform wurde gewählt, um die Induktivität zu minimieren und die elektrische Kontaktfläche für die Stromleitung zu maximieren.

Die Vermaschung war ultrafein, um die frequenzabhängigen Oberflächen- und Näherungseffekte zu berücksichtigen. In die Struktur wurde ein komplexwertiger Teststrom-Phasor mit einer Frequenz von 500 kHz injiziert. Da Vtest = ZTh Itest, beträgt die resultierende Spannung aufgelöst durch die FEA über den Eingangs-Ausgangs-Port des Moduls hinweg Vtest = ZTh. Der Streuinduktivitätswert wird mittels Im{ZTh} = Im{Vtest} = jωLσ Ω = 1,11014 × 10E-2 Ω berechnet. Die Auflösung für Lσ beträgt

3,53 nH.

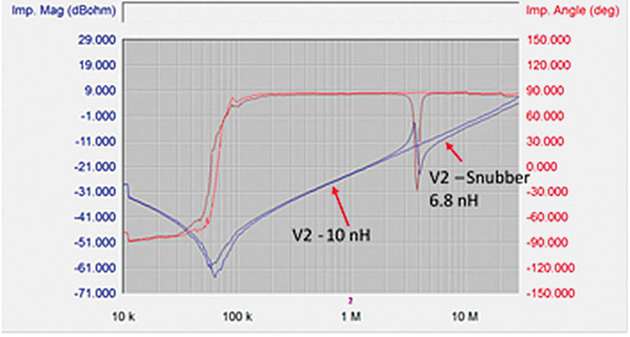

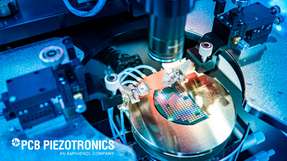

Um die Induktivität der laminierten DC-Busstruktur mit den obigen FEA-Ergebnissen zu vergleichen, hat Wolfspeed eine Kleinsignal-Impedanzmessmethode mit einem Impedanzanalysator mit hoher Bandbreite angewendet. Die Abbildung auf der vorherigen Seite zeigt die Testergebnisse der Kleinsignal-Impedanzmessungen der gesamten Kommutationsschleife an den Modulanschlüssen. Es sind zwei Magnituden- und Phasenverläufe mit und ohne kapazitiver Dämpfungsschaltung abgebildet.

Basierend auf den Ergebnissen resonieren die Kondensatoren und ihre Eigeninduktivität zusammen mit der Induktivität des Bus-Netzwerks bei etwa 60 bis 65 kHz. Die verwendete Testausrüstung kann sehr kleine Impedanzen nicht genau messen, so dass die Resonanzüberhöhung nicht präzise erfasst wurde. Die sehr niedrige Impedanz auf der Eigenfrequenz zeigt jedoch, dass die Sammelschiene und die Kondensatoren einen sehr niedrigen äquivalenten Serienwiderstand aufweisen. Die Kommutierungsinduktivität wurde berechnet (Lσ), nachdem die Messergebnisse der Eigenresonanzfrequenz (fSRF) vorlagen. Anhand von Messungen mit und ohne die stabförmigen Z-Achsen-Verbindungen ergab sich ein Induktivitätswert von etwa 5 nH. Die sechs DC-Bus-Folienkondensatoren wurden mit einem durchschnittlichen ESL von jeweils etwa 18 nH gemessen, die sechs parallelen ergaben einen effektiven Bank-ESL von etwa 18 nH / 6 = 3 nH. Die Gesamtinduktivität ohne Dämpfungsschaltung, gerundet auf den nächsten ganzen nH-Wert, betrug 11 nH.

Subtrahiert man die Induktivität der Zwischenkreiskondensatoren und der Z-Achsen-Verbindungen von der Gesamtinduktivität, so ergibt sich eine Schätzung für den laminierten DC-Bus allein: 11 nH – 3 nH – 5 nH = 3 nH. Dies liegt innerhalb von 15 Prozent des FEA-Ergebnisses. Die Induktivität ist mit dem NPO-Snubber bis etwa

4 MHz praktisch identisch über die Frequenz. In jedem Fall ist die laminierte DC-Bus-Induktivität mit oder ohne kapazitiver Dämpfungsschaltung sehr klein. Der niedrige Wert wurde durch eine kleine 0,23-mm-Trennung zwischen den Platten, eine hohe Stromüberlagerung sowie lange und breite (stabförmige) Abstandshalter anstelle von mehreren zylindrischen Stiften erreicht, die die Struktur mit den Leadframes des Leistungsmoduls verbinden.

Test ermittelt RMS-Laststrom

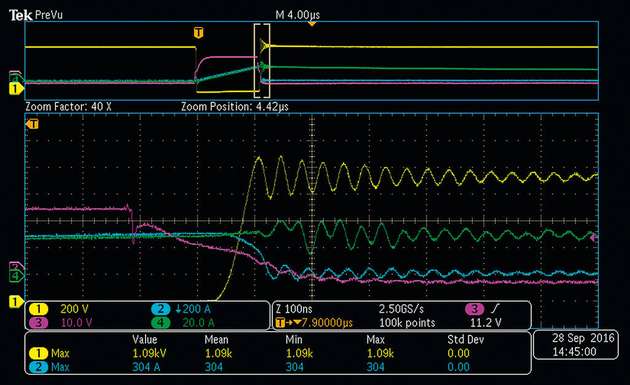

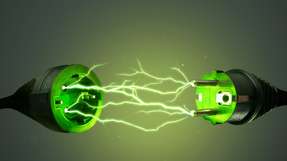

Ziel des Doppelpulstestes ist es, für eine DC-Bus-Spannung, mit 800, 850 und 900 V, den maximalen RMS-Laststrom für den gewählten externen Gate-Widerstand am Gate-Treiber zu bestimmen. Die Überhöhung ΔVovershoot = - Lσ di/dt trägt zur DC-Bus-Spannung bei der Abschaltung bei. Die Streuinduktivität Lσ ergibt sich aus dem ESL der Zwischenkreiskondensatorbank, der effektiven Streuinduktivität des laminierten DC-Bussings und der inneren Streuinduktivität der Leistungsmodule. Bei diesem Test wird dt durch den gewählten externen Gate-Widerstand bestimmt. Wenn di steigt, steigt außerdem ΔV hin zur maximalen Bemessungsspannung des Leistungsmoduls, also bis 1.200 V.

In diesem Test ist die DC-Bus-Spannung auf 900 V begrenzt und beinhaltet eine Überhöhung auf 1.100 V, was eine Marge von 100 V zulässt, bevor ein Lawinendurchbruch am Modul ausgelöst wird. Die nebenstehende Abbildung zeigt die RMS-Stromkapazität des Wechselrichters für eine DC-Bus-Spannung von 900 V, wobei die Schalterstellungs-

Spannungsüberhöhung auf 1.100 V

bei einem Abschaltstrom von 304 A begrenzt ist.