Mit der Einführung der Standards PCI Express 3.0 und 4.0 wurden mehrere optionale Funktionen wie Address Translation Services (ATS) und TLP Processing Hints (TPH) eingeführt. Diese fortschrittlichen Funktionen verbessern das Endpunkt-Verhalten und optimieren dadurch die Systemleistung. In Kombination mit einem komplementären Host können diese hochentwickelten Endpunkte das gesamte Busverhalten verbessern. Parallel dazu gibt es von ARM kontinuierlich Architekturverbesserungen, die dem Eco-System um die beiden Architekturen System Memory Management Unit (SMMU)

und Generic Interrupt Controller (GIC) sowie die AMBA-Protokolle von ARM zur Verfügung gestellt werden. Diese System-on-Chip-Architekturfunktionen (SoC) sind für die Unterstützung der PCIe-Protokolle notwendig.

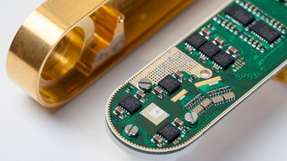

Es ist wichtig, diese Notwendigkeit für eine optimale PCIe-Performance in Enterprise-SoC-Anwendungen zu verstehen. In Enterprise-SoC-Anwendungen ist die PCIe-Schnittstelle die primäre Verbindung zwischen den Anwendungs-Prozessoren und den I/O-Geräten wie SSD, Gigabit-Ethernet und anderen High-Speed-Schnittstellen. Eine unzureichend funktionierende PCIe-Schnittstelle kann einen Engpass im System darstellen und die gesamte Systemleistung entscheidend beeinflussen. Der Anspruch an eine optimale Performance in Verbindung mit der komplexen Herausforderung einer funktionellen Integration von IP in das System ist der Grund dafür, dass die Integrationsverifikation und System-Performance-Analyse so schwierig sind.

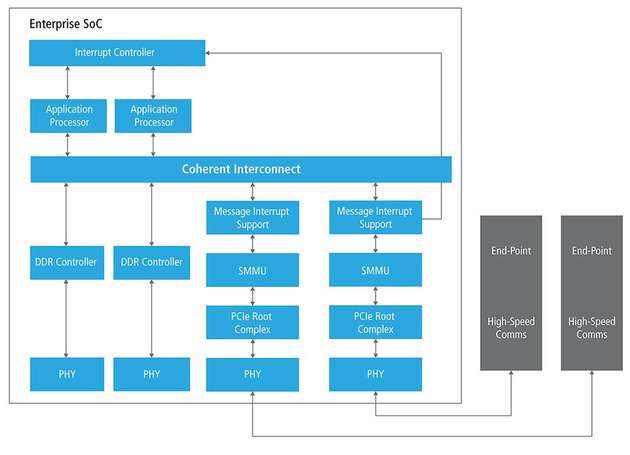

Das Blockdiagramm auf der nachfolgenden Seite zeigt die Schlüsselkomponenten eines typischen Enterprise-SoCs, wie er etwa in Servern verwendet wird. Das sind mehrere A-Class-ARM-Prozessoren, ein ARM-Interconnect mit Unterstützung für Cache-Stashing, ein verteiltes SMMU für eine I/O-Virtualisierung, ein verteilter Interrupt-Controller zur Unterstützung einer Interrupt-Virtualisierung, ein DDR-Speicher-System und natürlich eine IP für PCIe-Root-Complex-Controller und PHY. Der IP-Stack, der die PCIe-Schnittstelle mit dem Rest des SoC verbindet, verdeutlicht die Komplexität eines derartigen Systems.

Komplexere Verifikation durch Cache Stashing

Transaktionen zwischen dem Endpunkt und dem SoC sind grundsätzlich Schreib- und Leseoperationen von und zum Speichersystem. Jedoch gibt es zusätzliche Komplexitäten. Zum Beispiel kann ein Endpunkt wissen, dass ein Teil der Daten, die in den Speicher des SoC geschrieben werden sollen, nur kurz vom SoC genutzt und anschließend gleich verworfen wird. Um die Systemleistung zu optimieren, kann der Endpunkt Verarbeitungshinweise zu einem bestimmten Transport Layer Packet (TLP) hinzufügen. Das Root-Complex-IP ist dabei so konfiguriert, diese Attribute auf Seitenband-AMBA-Signale zu leiten, während die Daten zum Interconnect weitergeleitet werden. Wenn das Interconnect Cache Stashing unterstützt, teilen diese Attribute der Verbindung mit, dass die Daten in den Cache und nicht in den Arbeitsspeicher zu schreiben sind. Nachfolgende Software kann die Daten aus dem Cache nutzen und dann verwerfen, was insgesamt die Leistungsaufnahme und zeitaufwendiges Schreiben in den Arbeitsspeicher einspart. Diese relativ einfache Optimierung erhöht die Komplexität der Integrationsverifikation beträchtlich.

Ein weiteres Schlüsselelement der Architekturkomplexität ist die Unterstützung für ATS, eine in den fortschrittlicheren PCIe-Standards eingeführte Funktion. Da Endpunkte intelligenter werden und hoch entwickelte Verarbeitungsfähigkeiten enthalten, ist es wahrscheinlich, dass es innerhalb des Endpunkts MMU-Fähigkeiten geben kann. Das Weitergeben von Seitentabellen zwischen dem Haupt-SoC und dem Endpunkt mittels einer Hardware-Unterstützung ist das Ziel von ATS. Die Root-Complex-IP kann eine Seitentabellen-Anforderung erkennen und durch eine neue Verbindung zwischen dem PCIe-IP und den SMMU-Seitentabellen anfordern, die dann zum auslösenden Endpunkt übertragen werden. Der Endpunkt kann dann TLPs mit bereits umgerechneten Adressen erzeugen und sie mit Attributen versehen. Der Host-SMMU

erhält die Mitteilung, dass diese nicht umgerechnet, sondern nur durchgeleitet werden müssen. Das vermeidet zusätzliches Durcharbeiten von Seitentabellen auf der Host-Seite, da sich große Datenmengen ohne zusätzliche Adressumrechnung übertragen lassen. Das erzeugt allerdings zusätzlichen Verkehr, da die auf dem Host ausgeführten Cache-Wartungsoperationen nun auch auf die MMU im Endpunkt ausgedehnt werden.

Interrupt-Virtualisierung unterstützen

Die neueste GIC-Architektur von ARM bietet Unterstützung für die Interrupt-Virtualisierung. Diese virtuellen Interrupts werden in einem sehr ähnlichen Mechanismus umgesetzt, den die SMMU für die Adressumrechnung nutzt. Interrupt-Umsetzungstabellen werden im Speicher abgelegt sowie im Interrupt-Controller zwischengespeichert. Sobald ein virtueller Interrupt eingeht und die Umrechnungsseite nicht im Controller ist, wird ein sogenannter Table Walk wie bei einem MMU-Verhalten ausgelöst.

Einige der hochentwickelten Merkmale, die für ein sehr leistungsfähiges PCIe-Verhalten erforderlich sind, wurden bereits vorgestellt. Die Herausforderung für die Integration besteht darin, dass es jetzt unter anderem komplexe Hardware-Verbindungen zwischen dem PCIe-IP und dem SoC-System sowie Verbindungen zwischen dem Endpunkt und dem System-MMU gibt. Ursprünglich war die Integrationsverifikation ein vergleichsweise einfaches Verfahren, da nur überprüft werden musste, ob die AMBA-Schnittstelle von ARM korrekt angeschlossen ist. Jetzt ist eine beträchtliche Software- Unterstützung notwendig, um das System überhaupt in einen Status zu bekommen, in dem die hochentwickelte Funktionalität ausgeübt werden kann. Um hinreichend sicherzustellen, dass es sich korrekt verhält, muss eine Reihe von Anwendungsfällen definiert und eine Testumgebung aufgebaut werden. Diese Fälle müssen außerdem erfasst und ausgeführt sowie die Endpunkte geprüft werden.

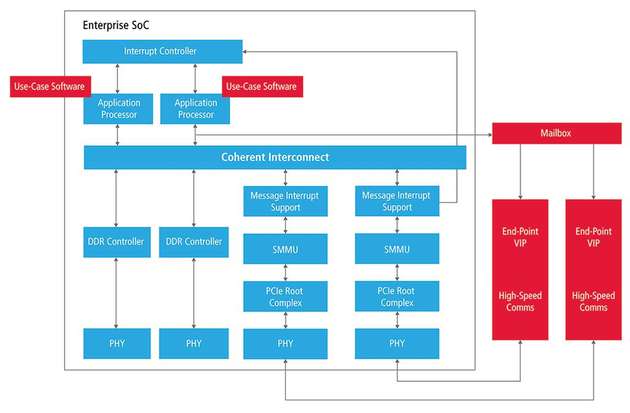

Diese Kombination von Software- und Hardware-Verifikation ist eine Herausforderung. Der Umfang der erforderlichen Software hat die Unternehmen nun bewegt, nach Lösungen zu suchen. Außerdem hat die konventionelle Simulation, die lange die tragende Säule der Verifikation war, zu kämpfen, wenn das gesamte SoC und die Software zusammen verifiziert werden. Die Nutzung von Hardware-Beschleunigern hat in den letzten Jahren drastisch zugenommen, was eine weitere Herausforderung darstellt. Um die Integrationsverifikation durchzuführen, wird zuerst eine passende Testumgebung mit Hilfe entsprechender Verifikations-IPs für die Endpunkte erstellt und über eine Speicher-gemappte Mailbox gesteuert. Auf diese Weise kann die auf den Prozessoren laufende Software sowohl die SoC-Hardware als auch den extern erzeugten Endpunkt-Verkehr steuern. Die echte He-

rausforderung besteht allerdings darin, die Software zu erstellen, um die gewünschten Anwendungsfälle zu modellieren.

Accellera Portable Stimulus Standard

In den letzten Jahren wurde unter Führung von Accellera mit der Definition eines Standards für portierbare Stimuli (Portable Stimulus) begonnen. Der Portable-Stimulus-Standard ermöglicht es, das Systemverhalten abstrakt zu modellieren. Dadurch lassen sich Anwendungsfälle unabhängig von der zu Grunde liegenden Plattform erstellen. Unter Verwendung dieser Technologie konnte Cadence eine umfassende Bibliothek für die PCIe-Integration aufbauen. Diese stellt umfassende Standard-Fähigkeiten bereit, die von Software, externer Verifikations-IP oder externer Accelerated-VIP für die Hardware-Beschleunigung gesteuert werden können. Auf diese Weise kann jede Kombination von Root-Complex oder Endpunkt-Integration mit oder ohne Prozessor unterstützt werden. Im Fall eines fortschrittlichen PCIe-Verhaltens kann dies den Zeitaufwand für die Integration der Systeme deutlich verkürzen.

Die Bereitstellung des Stimulus allein ist nützlich, aber umfasst nicht alle erforderlichen Fähigkeiten. Ein umfassender Verifikationsplan ist Teil des Gesamtpakets, das eine schnelle Modellierung, eine eingeschränkte Erzeugung zufälliger Anwendungsfälle und eine Erfassung der Abdeckung sowie eine automatische Zuordnung auf dem Plan erlaubt. Dadurch wird eine einfache Messung des Projekts bis zum Abschluss ermöglicht.

Performance-Verifikation

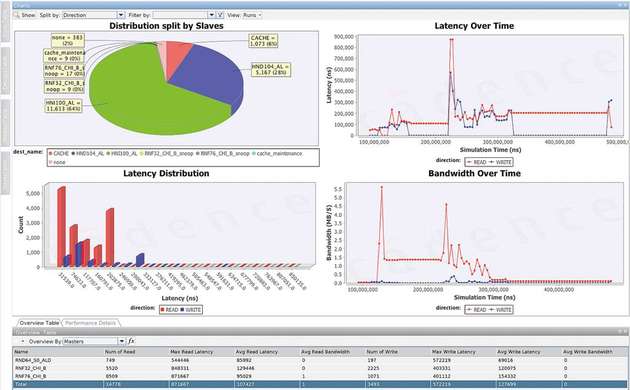

Allein die Verifizierung der funktionellen Korrektheit des SoC ist eine komplexe, aber lösbare Aufgabe. Die Performance stellt allerdings einen großen Teil der Herausforderung dar. Die Validierung, dass das SoC nur minimal durch PCIe gedrosselt wird, ist eine ebenso wichtige Aufgabe. Die Stärke der Use-Case-Software-Generierung besteht darin, dass sowohl Funktions- als auch Performance-Belastungstests erstellt und ausgeführt werden können. Die obige Abbildung zeigt die Ergebnisse dieser Performance-Analyse für einen kleinen Anwendungsfall, der auf einem Palladium-Hardware-Beschleuniger von Cadence ausgeführt und mittels eines AVIP-Monitors ausgelesen wurde. Zuerst wurden die Latenz- und Bandbreitenwerte erfasst, anschließend lässt sich eine umfassende Analyse für einen oder mehrere Tests ausführen und die Ergebnisse können verglichen werden.

Differenzvergleiche der gleichen Tests, die auf verschiedenen Systemkonfigurationen, Cache-Größen, Taktgeschwindigkeiten und DDR-Standards laufen, lassen sich damit einfach durchführen. Die SoC-Entwickler können die Systemkonfiguration vor dem RTL-Tapeout umfassend analysieren. Das ist besonders im Bereich von Enterprise-SoCs wichtig, weil es bisher beträchtlich schwieriger war, solche Ergebnisse schnell zu erhalten. Mit hoch entwickelten Analyse-Tools ist nun auch ein tiefer Einblick in das Systemverhalten unter Last mit Software-Workload und einem gleichzeitig hohem PCIe-Verkehr möglich.