Low-Side-Gate-Treiber-ICs werden häufig in Schaltnetzteilen eingesetzt. Sie sorgen dafür, dass die Leistungs-MOSFETs beim Ein- und Ausschalten sauber angesteuert werden. In Aufwärtswandlern mit Leistungsfaktorkorrektur (Boost-PFC) treiben sie den Hochvolt-MOSFET auf der Low-Side. In Hochvolt-DC/DC-Stufen wie LLC (Resonanzwandler), ZVS (Zero Voltage Switching) und TTF (Two Transistor Forward) schalten sie über einen Puls-Transformer die Hochvolt-MOSFETs. In synchronen Gleichrichter-Stufen sind sie direkt mit den Niederspannungs-MOSFETs verbunden.

Die Eingangssignal-Level von konventionellen Low-Side-Gate-Treiber-ICs beziehen sich auf das Massepotenzial des Gate-Treibers. Parasitäre Induktivitäten auf der Masseleitung zwischen dem Gate-Driver-IC und dem Controller-IC sowie im Source-Pfad des Power-MOSFETs sind häufig die Ursache für eine Verschiebung des Massepotenzials des Gate-Drivers, sobald der Power-MOSFET schaltet. Diese Verschiebung des Massepotenzials, der sogenannte Ground Shift, kann zur Fehlansteuerung des Power-MOSFETs führen. Das beeinträchtigt die Leistungsfähigkeit des Schaltnetzteiles deutlich. Im Extremfall überlastet das eine Halbbrücken-Schaltung und zerstört die damit verbundenen MOSFETs.

Amplituden von bis zu ±70 V

In hart schaltenden Topologien wie Boost-PFCs oder TTF-Leistungsstufen erfordern die parasitären Induktivitäten im Source-Anschluss des Leistungs-MOSFETs und im Massepfad der Leiterplatte von Entwicklern eine besondere Aufmerksamkeit. Mit hart schaltend sind hohe dI/dt-Werte gemeint, die zu Schaltrauschen auf Massepotenzial führen. Bei diesem Rauschen handelt es sich um eine Hochvoltschwingung im Bereich von 50 bis 120 MHz, mit Amplituden bis zu ±70 V. Häufig ist es verantwortlich für die transiente Verschiebung des Massepotenzials zwischen dem Controller- und dem Gate-Treiber-IC. Dieser Effekt tritt umso stärker auf, je größer die Ausgangsleistung des Schaltnetzteils ist. Oftmals verschärft sich die Situation wegen suboptimaler Auswahl der Leiterplatten oder auf Grund der Designvorgaben des Produkts, in dem das Schaltnetzteil eingebaut ist.

Die Lösung für dieses Problem ist komplex. Grundsätzlich gilt, je geringer die parasitären Induktivitäten in der Leistungsschleife sind, desto geringer sind auch die induzierten Masseoszillationen, und die Gefahr von unerwünschtem Triggern sinkt. Um unerwünschten Ground Shift des Gate-Driver-ICs zu minimieren, stehen Entwicklern verschiedene Optionen zur Verfügung. Sie können zum Beispiel die dynamische Gate-Schleife auf eine sehr kleine Fläche der Leiterplatte beschränken und auf ihr spezielle niederimpedante GND-Leiterbahnen verwenden. Ebenfalls hilfreich ist der Einsatz von Power-MOSFETs mit Leadless-Gehäusen oder separaten Kelvin-Source-Anschlüssen.

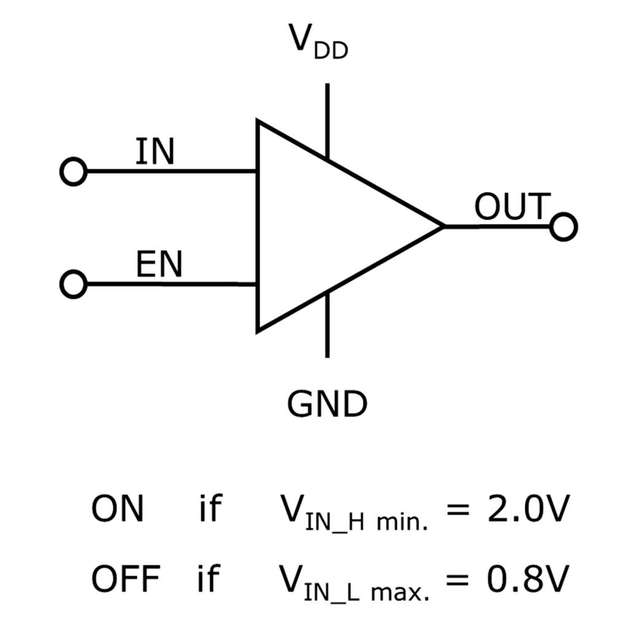

Konventionelle Low-Side-Gate-Treiber sind anfällig gegen Masseverschiebungen. In einem konventionellen Low-Side-Gate-Treiber erfolgt die Interpretation der Steuer- und

Enable-Input-Signale immer durch einen Vergleich der Eingangsspannung und des Massepotenzials des Gate-Treiber-ICs. Im Beispiel in Abbildung 1 ist der Eingang so lange auf logisch „Off“, wie das Eingangssignal nicht höher als 2,0 V

gegenüber der Masse ist. Entsprechend ist der Eingang auf logisch „On“, bis das Eingangssignal auf 0,8 V gegenüber dem Massepotenzial abfällt.

Werden die Eingangssignale auf gleichem Potenzial belassen, aber das Massepotenzial des Gate-Treibers verschoben, dann entsteht ein Problem. Üblicherweise sind die Eingänge des Gate-Treibers mit einem Controller-IC verbunden. Aus Sicht des elektrischen Designs ist dieser in Hinblick auf die Stabilität des Massepotenzials dem Gate-Treiber-IC überlegen. Das Problem verschärft sich, falls sich der Massekontakt des Gate-Treibers relativ weit weg vom Massekontakt des Controllers befindet. Das kann beispielsweise der Fall sein, wenn der Controller auf einer Tochterkarte untergebracht wurde.

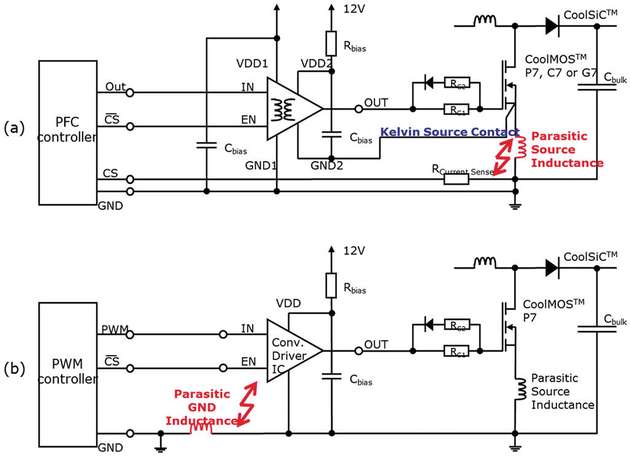

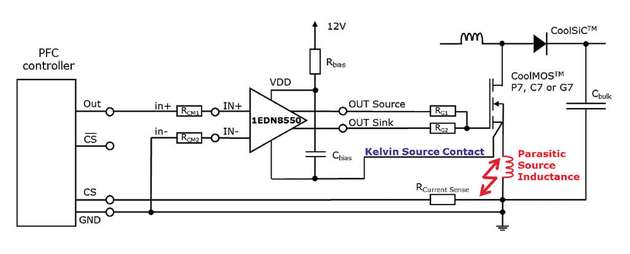

Abbildung 2a zeigt eine Boost-PFC-Schaltung mit einem Leistungs-MOSFET und einem Kelvin-Source-Kontakt. Üblicherweise werden die beiden Massepotenziale über einen galvanisch isolierten Gate-Treiber entkoppelt. Das bedeutet, der Controller-IC und die Eingangsseite des Gate-Treibers (GND1) sind von der Ausgangsseite des Gate-Treibers (GND2) elektrisch getrennt. Das nennt man Durchtrennung der Masseschleife (cutting the ground loop).

Der Kelvin-Source-Kontakt in Abbildung 2a wird dazu genutzt, den Einfluss der parasitären Source-Induktivität des MOSFETs auf das Masse-Potenzial des Gate-Treibers zu reduzieren. Messungen für derartige Topologien haben ergeben, dass die Oszillationen zwischen der Masse des PWM-Con-

trollers und der Ausgangsseite des Gate-Treibers immer noch

±60 V erreichen können.

In Stromversorgungen im Bereich Low Power geht es nicht nur um die höchste Leistungsfähigkeit. Oft sind die mechanischen Designanforderungen und die Kosten der Komponenten- und Leiterplatten relevanter. Deshalb können die idealerweise gewünschten Abstände zwischen dem Controller und dem Gate-Treiber in vielen Fällen nicht eingehalten werden. Entwickler sind dadurch manchmal gezwungen, Leiterplatten mit nur einer Lage einzusetzen und keine isolierten Gate-Treiber zu verwenden. Häufig sind hohe parasitäre Masseinduktivitäten die Folge, wie zu sehen in Abbildung 2b. In derartigen Anwendungen kann das Schalten eines MOSFETs schnell zu einem Versatz des Massepotenzials von bis zu ±20 V zwischen dem PWM-Controller und dem Gate-Treiber führen.

Differenzielle Steuereingänge: Unabhängigkeit vom Massepotenzial

Verfügt ein Gate-Treiber-IC über echte differenzielle Eingänge, dann sind die Steuersignale weitgehend unabhängig vom Massepotenzial des ICs. Denn nur die Spannungsdifferenz zwischen den Eingangskontakten ist relevant dafür, ob der Ausgang auf On oder Off geschaltet wird. Ist zum Beispiel das Potenzial von Vin+ um mehr als 1,8 V höher als das Potenzial von Vin-, dann wird das als logisch On interpretiert. Beträgt die Differenz weniger als 1,5 V, dann wird das als logisch Off interpretiert.

Die EiceDRIVER 1EDN7550B und 1EDN8550B von Infineon sind einkanalige Low-Side-Gate-Treiber, die statische Ground-Shift-Probleme bis zu ±70 V verhindern können. Ist der Ground Shift transient – was typisch ist für das Masserauschen, das durch schaltende MOSFETs verursacht wird –, dann sind die Gate-Treiber-ICs sogar robust bis zu ±150 Vpeak. Die Steuereingänge der Gate-Treiber-ICs verfügen über eine hohe statische und dynamische Gleichtakt-Common-Mode-Immunität.

Beim Platinenlayout wird empfohlen, die beiden Common-Mode-Widerstände möglichst nah an den Eingangskontakten des Gate-Treiber-ICs zu platzieren. Das Layout sollte sowohl geometrisch als auch parasitär symmetrisch sein. Die Anschlussanordnung auf der Ausgangsseite und für den VDD-Anschluss entspricht gängigen einkanaligen Low-Side-

Gate-Treibern. Daher muss für ein Upgrade bestehender Designs mit dem 1EDN7550 oder dem 1EDN8550 nur die Eingangsseite auf der Leiterplatte modifiziert werden.

Die beiden Gate-Treiber-ICs sind in einem kleinen 6-poligen SOT-23-Gehäuse untergebracht. Das hilft im Vergleich zu galvanisch isolierten Gate-Treiber-ICs, die Leistungsdichte zu verbessern. Der Gehäusetyp bietet außerdem den Vorteil, dass der Entwickler die Gate-Treiber-ICs optimal zum Gate-Anschluss der Leistungs-MOSFETs platzieren kann.

Robust gegen Ground Shifts mit bis zu 150 V

Low-Side-Gate-Treiber-ICs mit echten differenziellen Steuereingängen, wie die 1EDN7550B und 1EDN8550B, sind robust gegenüber Ground Shifts mit bis zu ±70 V statisch und ±150 Vpeak dynamisch. Beide Betriebsparameter setzen ein entsprechendes Leiterplattenlayout voraus. Mit dem 1EDN7550B und dem 1EDN8550B kann ein einkanaliger Low-Side-Gate-Treiber genutzt werden, um Leistungs-MOSFETs mit Kelvin Source wie CoolMOS P7, C7 oder G7 in Anwendungen wie 2,5-kW-Boost-PFCs zu treiben.

1EDN7550B und 1EDN8550B bieten ausreichende Robust-

heit gegenüber Masseverschiebungen in Designs mit großen Abständen zwischen dem Controller-IC und dem Gate-Driver-IC. Low-Side-Gate-Treiber mit echten differenziellen Steuereingängen ermöglichen eine kürzere Entwicklungszeit, höhere Leistungsdichte und robustere und effizientere Designs – und das alles bei geringeren Kosten im Vergleich zu herkömmlichen Lösungen.