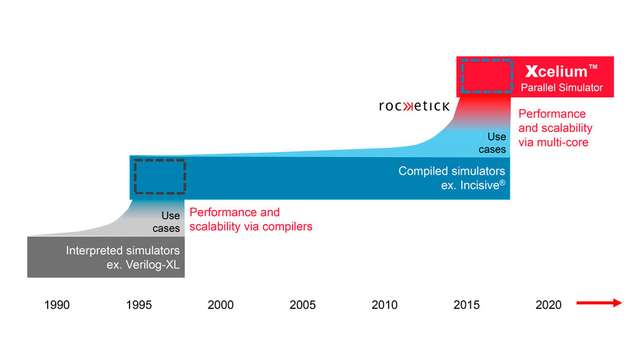

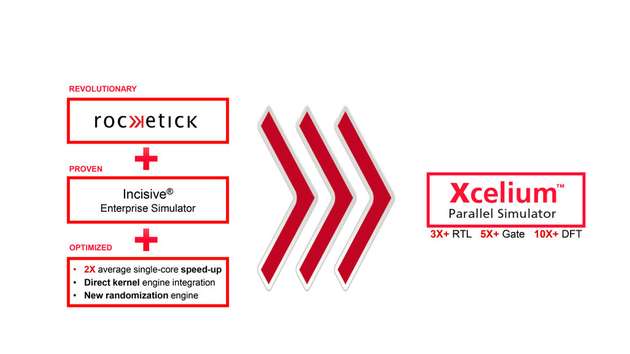

Cadence Design Systems präsentiert mit dem Xcelium Parallel Simulator laut Hersteller den ersten Simulator der dritten Generation, der sich bereits in der Produktion bewährt hat. Er basiert auf der parallelen Multi-Core-Rechentechnologie, mit der SoCs (System on Chip) schneller auf den Markt gebracht werden können.

Projektlaufzeiten verkürzen

Der Xcelium Simulator basiert auf der parallelen Simulationstechnologie, die von Rocketick übernommen wurde. Mehrere Funktionen helfen, die Laufzeit von Projekten um mehrere Wochen zu verkürzen: eine dreifach schnellere Design-Simulation auf RTL-Ebene (Register Transfer Level), eine fünffach schnellere Simulation auf Gate-Ebene und eine zehnfach schnellere parallele DFT-Simulation (Design for Test).

Neue Funktionen beschleunigen die SoC-Verifikation einschließlich der SoC SystemVerilog Testbench Abdeckung für ein schnelleres Abschließen der Verifikation und ein paralleles Multi-Core-Build.

Simulation passt sich den Gegebenheiten an

Der Xcelium Simulator unterstützt moderne Design-Stile und IEEE-Standards und ermöglicht so den Ingenieuren eine Leistungssteigerung ohne eine erneute Code-Erstellung. Zudem passt der Kompilations- und Entwicklungs-Flow des Xcelium Simulators den Design- und Verifikations-Testbench-Code den idealen Engines an und wählt automatisch die passende Anzahl von Cores für eine beschleunigte Ausführung aus.

.jpg)