Chips in industriellen Anlagen kommunizieren schon heute verschlüsselt miteinander. Viele Algorithmen könnten jedoch bald keinen Schutz mehr bieten, dann nämlich, wenn Cyberkriminelle Quantencomputer für ihre Angriffe nutzen.

Aus diesem Grund beschäftigen sich Sicherheitsexperten weltweit damit, technische Standards für eine Post-Quanten-Kryptografie zu entwickeln. Eine Herausforderung dabei sind die hohen Rechenanforderungen dieser Verschlüsselungsverfahren.

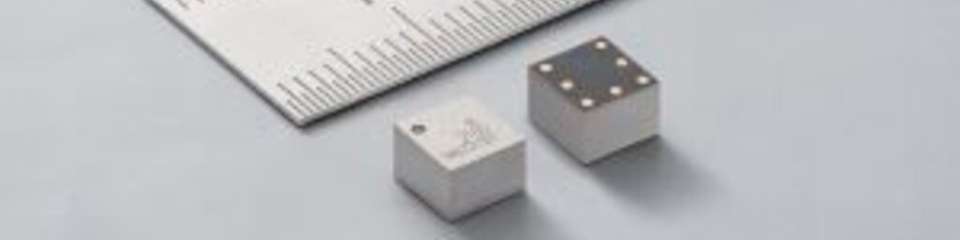

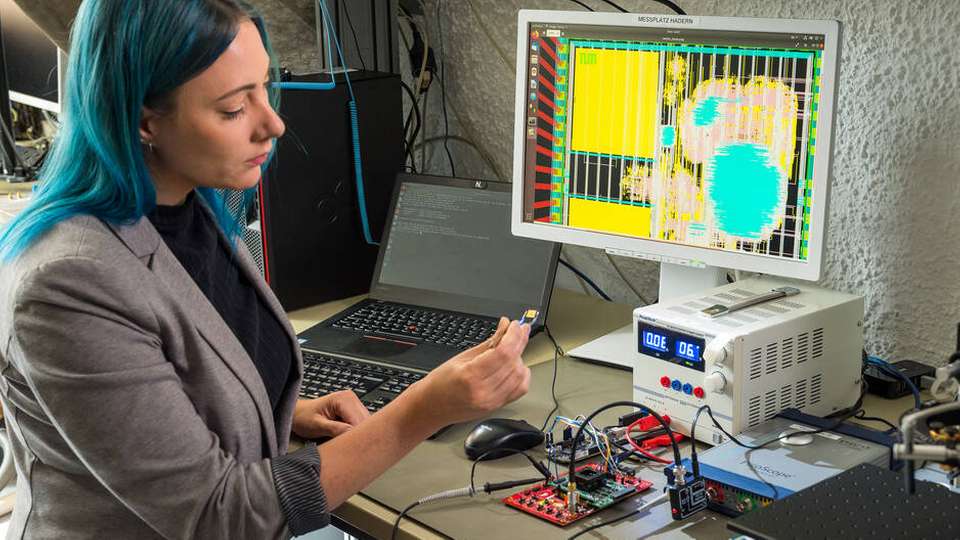

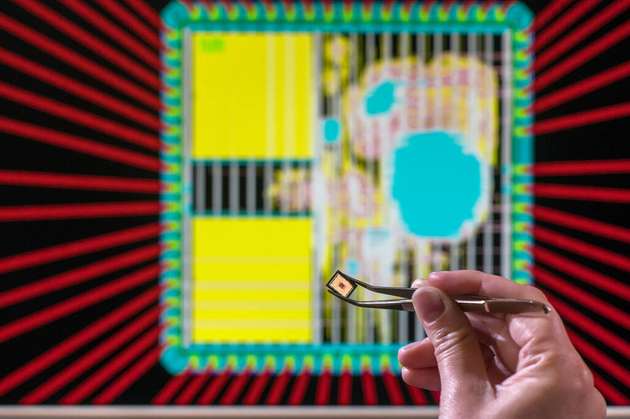

Ein Team um Georg Sigl, Professor für Sicherheit in der Informationstechnik an der TU München (TUM), hat jetzt einen Chip entworfen und fertigen lassen, der Post-Quanten-Kryptografie besonders effektiv umsetzen soll.

Kombination aus Hardware und Software

Sigl und sein Team setzen bei ihrem neuen Chip auf ein Hardware-Software-Co-Design. Dabei ergänzen sich spezialisierte Bauteile und Steuerungssoftware. „Unser Chip ist der erste, der für Post-Quanten-Kryptografie konsequent auf ein Hardware-Software-Co-Design setzt“, sagt der Professor.

Dadurch könne er Verschlüsselungen mit „Kyber“, einem aussichtsreichen Kandidaten für Post-Quanten-Kryptografie, etwa zehnmal so schnell umsetzen wie Chips, die reine Softwarelösungen nutzen. Laut Sigl verbraucht er dabei außerdem circa achtmal weniger Energie und ist fast genauso flexibel.

Open-Source-Standard als Basis

Bei dem Chip handelt es sich um eine anwendungsspezifische integrierte Schaltung, kurz ASIC. Das TUM-Team modifizierte dafür ein Open-Source-Chipdesign, das auf dem quelloffenen RISC-V-Standard basiert.

Post-Quanten-Kryptografie-fähig wird der Chip dann zum einen durch eine Modifikation des Rechnerkerns und besondere Instruktionen, mit denen notwendige Rechenoperationen beschleunigt werden. Zum anderen erweiterten die Münchener Forscher das Design um einen eigens entwickelten Hardwarebeschleuniger. Durch ihn ist der Chip in der Lage, neben gitterbasierten Postquanten-Krypografie-Algorithmen wie „Kyber“ auch mit dem Algorithmus „Sike“ zu arbeiten, der mit deutlich mehr Rechenaufwand verbunden ist.

So kann „Sike“ nach Angaben des Teams mit dem neuen Chip rund 21-mal schneller umgesetzt werden als mit Chips, die für die Verschlüsselung nur auf Software setzen. „Sike“ wird als erfolgversprechende Alternative gehandelt, sollten gitterbasierten Ansätze sich irgendwann als nicht mehr sicher erweisen. Das ist überall dort sinnvoll, wo Chips über einen langen Zeitraum eingesetzt werden.

Wirksam gegen Hardware-Trojaner?

Abgesehen von herkömmlichen Hackerattacken steigt in der Industrie auch die Bedrohung durch sogenannte Hardware-Trojaner. Computerchips werden in der Regel nach den Vorgaben von Unternehmen in spezialisierten Fabriken hergestellt: Hier könnten Angreifer vor oder während der Fertigung Trojaner-Schaltkreise in das Chipdesign schmuggeln.

Genau wie bei einem Hackerangriff von außen ließen sich so beispielsweise Fabriken lahmlegen oder Produktionsgeheimnisse stehlen. Mehr noch: Ist der Trojaner schon in der Hardware verbaut, lässt sich auch Post-Quanten-Kryptografie unterlaufen.

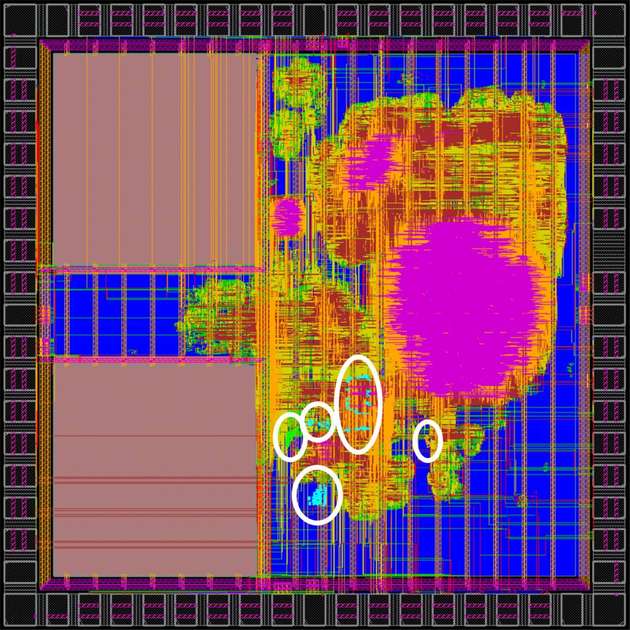

„Bislang wissen wir sehr wenig darüber, wie Hardware-Trojaner von realen Angreifern eingesetzt werden“, sagt Sigl. „Um Schutzmaßnahmen zu entwickeln, müssen wir uns gewissermaßen in Angreifer hineinversetzen und selbst Trojaner entwickeln und verstecken. In unserem Post-Quanten-Chip haben wir deswegen vier von uns entwickelte Trojaner eingebaut, die ganz unterschiedlich arbeiten.“

Zerstörung zu Forschungszwecken

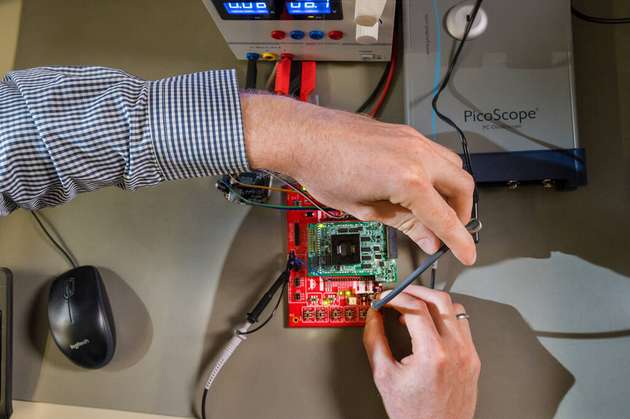

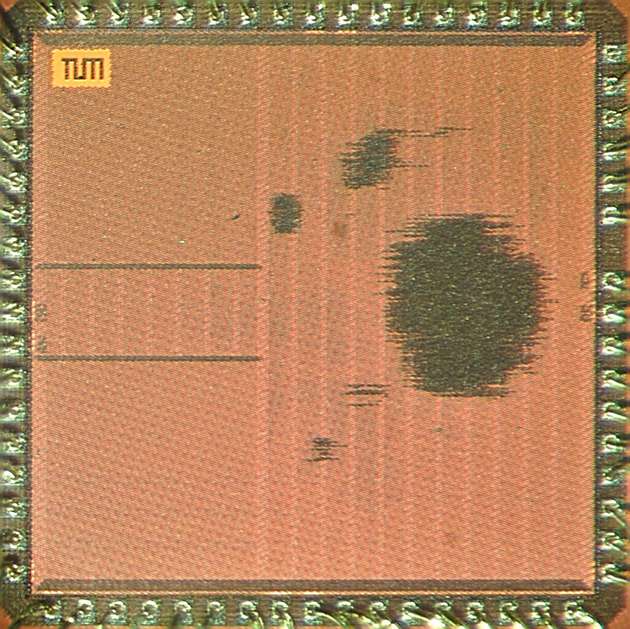

In den kommenden Monaten wollen Sigl und sein Team die Kryptografie-Fähigkeiten ihres Chips sowie die Funktion und Nachweisbarkeit von Hardware-Trojanern intensiv testen. Im Anschluss wird der Chip dann zerstört: In einem aufwendigen Prozess werden seine Leiterbahnen Schicht für Schicht abgeschliffen und jede einzelne davon fotografiert.

Auf diese Weise wollen die Forscher neue am Lehrstuhl von Sigl entwickelte KI-Verfahren erproben, mit denen sich die exakte Funktionsweise von Chips rekonstruieren lässt, auch wenn keine Dokumentation vorliegt. „Solche Rekonstruktionen können dabei helfen, Bestandteile eines Chips zu identifizieren, deren Funktion nichts mit dessen eigentlichen Aufgaben zu tun haben und die möglicherweise hineingeschmuggelt wurden“, erklärt Sigl.

Solche Verfahren könnten laut dem Professor einmal Standard für Stichproben bei großen Chip-Bestellungen werden. „Zusammen mit einer effektiven Post-Quanten-Kryptografie können wir so Hardware in Industrieanlagen, aber beispielsweise auch in Pkw sicherer machen.“