Das Entwickeln und Optimieren von elektrischen Schaltungen ist eine schwierige Aufgabe, weil allzu häufig unterschiedliche Vorgaben an die Schaltung zueinander im Widerspruch stehen. Die Schaltung soll zuverlässig, aber günstig sein. Für die elektrische Sicherheit und EMV sollen die Abstände groß sein, aber das Endgerät soll miniaturisiert werden. Ausführliches Simulieren, Messen und Testen stehen im Widerspruch zu einem schnellen Markteintritt und geringen Kosten.

Wenn der Elektronikentwickler eine Schaltung entwirft, so wählt er elektronische Komponenten aus und verbindet die Pins miteinander. Pins können Power oder Ground, Signale, differentielle Signale sein oder zu Bussen gehören. Alle Verbindungen werden in der PCB Design-Software als Netzliste für die Schaltung erfasst und im Schaltplan dokumentiert.

CAD-Software zugeschnitten auf den Nutzer

CAD-Software zum Entwickeln von Leiterplatten kann schon seit langem mit Design-Rule-Checks die Einhaltung von Vorgaben prüfen. Diese Checks waren bisher meist auf Überprüfungen der Vorgaben wie Leiterbahnbreiten, Leitungslängen und Abstände aller Art im Layout der Leiterplatte fokussiert. Über die Jahre wurden die Regeln, die in Echtzeit beim Routen geprüft werden, um viele Vorgaben im Hinblick auf Signalintegrität erweitert.

Durch die Miniaturisierung werden die Fertigungstoleranzen weiter ausgereizt und es sind in den letzten Jahren DFM-Checks im Layout ergänzt worden. Mit diesen DFM-Checks lassen sich online während des Layoutens die Vorgaben eines Unternehmens für die unterschiedlichen Maschinen in der Fertigung bereits mitberücksichtigen.

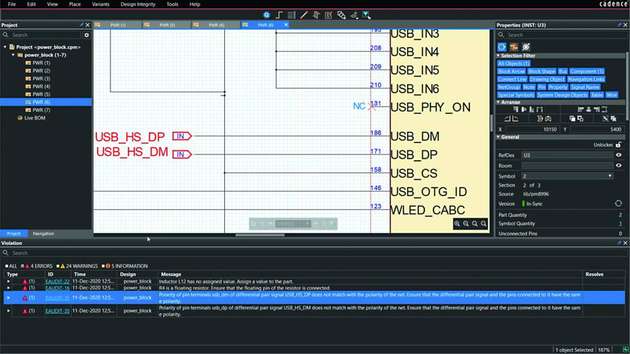

Mit dem letzten Release des Schaltplaneingabe-Tools Allegro System Capture kommt eine ganz neue Kategorie von Audits bereits im Schaltplan hinzu. In weltweiten Gesprächen und Umfragen unter den Entwicklern hat sich herausgestellt, dass es durch Komplexität und Zeitdruck zu immer mehr Flüchtigkeitsfehlern in den Designs kommt.

In manuellen, optischen Design Reviews sollen diese Fehler gefunden werden. Aber Fehler wie falsch dimensionierte Pull-Up-Widerstände oder falsche Spannungswerte an Kondensatoren sind sehr schwer zu erkennen. Wegen steigender Anforderungen und sinkender Toleranzen sind sie oft die Ursache für sporadische Ausfälle oder unzuverlässige Leiterplatten.

Audits im Schaltplan

Mit Audits im Schaltplan kann die Qualität der Schaltung und damit die Zuverlässigkeit der Baugruppe erhöht werden. Die Audits geben dem Entwickler ähnlich wie eine Rechtschreibprüfung in der Textverarbeitung sofortiges Feedback, wenn Regeln verletzt wurden. In der Rechtschreibprüfung werden nicht nur falsch geschriebene Worte durch Vergleiche mit einem Wörterbuch gefunden, sondern es werden auch Fehler bei Satzzeichen oder Grammatik erkannt. Solche „Grammatikfehler“, die über bisherige Schematic Rule Checks hinausgehen, gibt es auch in der Elektronik.

In Audits wird mit der Netzliste und den Informationen aus der Bauteilbibliothek die Schaltung systematisch analysiert. Es werden falsch angeschlossene Pins von der Software erkannt, wenn zum Beispiel ein Power- oder Ground-Pin an einen falschen Spannungswert angeschlossen wird. Das Tool kann auch erkennen, wenn es sich um einen Anschluss über einen Spannungsteiler, Pull-up- oder Pull-down Widerstand handelt.

Es werden auch Stellen hervorgehoben, an denen eine Leitung (Netz) beispielsweise nur an einem Pin angeschlossen ist. Zu solchen Fällen kann es kommen, wenn Schaltungen über mehrere Seiten mit Off-Page-Symbolen verbunden werden und hier die Leitung am Übergang von Schaltplanseiten unterbrochen wurde. Solche Fehler sind schwer zu sehen, jedoch im CAD-Tool schnell zu prüfen. Die Audits erkennen aber noch viel mehr und die Suchkriterien gehen deutlich über bisherige Checks und Analysen hinaus.

Präzisere Fehlererkennung als bisher

So kann auch verifiziert werden, ob der Wert eines Pull-Up- oder Pull-Down-Widerstands zur Schaltung und zur Betriebsspannung passt. Fehler durch falsche Widerstandswerte sind vom Entwickler sehr schwer zu erkennen und führen zu Signalfehlern oder zu hohem Stromverbrauch. Solche Fehler in einer Schaltung beim Review zu finden ist äußerst schwierig.

Die Unterscheidung zwischen eindeutigen Fehlern, Warnungen und Informationen hilft dem Entwickler bei der Gewichtung der Meldungen. Die Probleme werden in einer Liste sortiert nach Kategorie, Fehlern und Warnungen angezeigt. Wenn der Entwickler einen Eintrag auswählt, zoomt Allegro System Capture an die relevante Stelle im Schaltplan. Durch die entsprechenden Hinweise weiß der Entwickler sofort, was zu tun ist, um den Fehler zu beheben.

Wenn fälschlicherweise ein NC-Pin an Ground angeschlossen wird, kann das zu Problemen in der Zuverlässigkeit führen. Zu Non Connected Pins an ICs kommt es, wenn ein Standard IC-Gehäuse mehr Pins hat wie für die Funktion benötigt wird und aus Kostengründen kein eigenes IC-Gehäuse entwickelt wird, oder wenn Pins in der IC-Fertigung zum Kalibrieren oder Programmieren verwendet werden.

NC-Pins werden entweder nicht genutzt, dann wäre es nur eine überflüssige Verbindung im Layout, die Platz verbraucht und gegebenenfalls einen „Stub“ darstellt und als EMV-Antenne für Ein- und Abstrahlung fungiert. Aber wenn dieser NC-Pin für die Programmierung oder die Kalibrierung bei der Herstellung der Komponente verwendet wird, könnten Spannungsänderungen an diesem Pin den Baustein in einen anderen Modus versetzen und die Funktion der ganzen Baugruppe beeinträchtigen.

Stress von Bauteilen

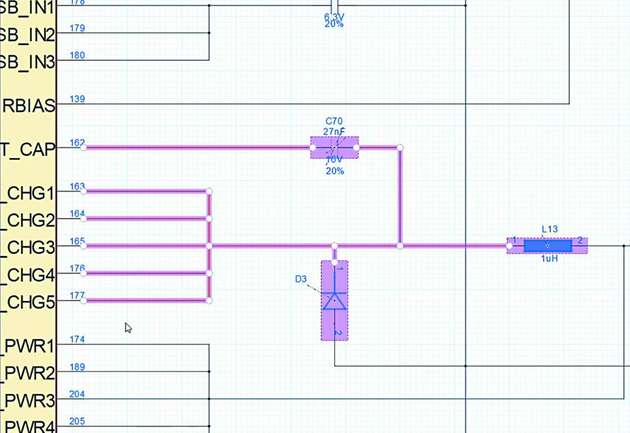

Durch eine Simulation im Hintergrund können die Ströme berechnet werden, die durch Bauteile fließen. Ein Vergleich mit den maximal zulässigen Strömen, die für das Bauteil in der Bibliothek hinterlegt wurden, dient als Grundlage für eine Stressanalyse.

Das Tool erkennt die Bauteilart und kann so ein Default-Model für die Simulation mit den Bauteilwerten automatisch anpassen. Wenn PSpice Modelle hinterlegt werden, können die Ergebnisse sogar noch verfeinert werden. Für die Stress-Analyse muss der Entwickler nichts vorbereiten. Alle erforderlichen Werte sollten bereits in der Bibliothek verfügbar sein. Sollte doch ein benötigter Wert fehlen, so würde dies als Warnung angezeigt werden und nach der Eingabe behoben sein.

Gerade in der Leistungselektronik ist der maximale Strom, der durch ein MOSFET oder IGBT fließt, wichtig für die Zuverlässigkeit einer Schaltung. Gestresste Bauteile können frühzeitig ausfallen oder es kommt durch Überlastung zu Fehlfunktionen. Das Audit stellt die Belastung der Bauteile in Prozent dar und es kann ohne großen Aufwand erkannt werden, welche Bauteile in der Schaltung am meisten und welche nur gering belastet werden.

Da überlastete Bauteile im Laufe der Zeit ausfallen können, sind diese Hinweise auf die Belastung der Bauteile schon früh im Entwicklungsablauf sehr hilfreich. Der Entwickler kann sofort durch Änderungen in der Schaltung oder durch belastbarere Bauteile Abhilfe schaffen. Dies stellt die kostengünstigste Methode dar, da Fehler frühzeitig vermieden oder sofort behoben werden, bevor Folgekosten durch Prototypen und Redesigns entstehen.

Für die Analyse wird die Schaltung im Hintergrund in Teilschaltungen (Subcircuits) aufgeteilt. Wenn im Report ein gestresstes Bauteil angezeigt wird, dann können diese Teilschaltungen angezeigt werden, die alle relevanten Bauteile für die Überlastung enthalten. Der Entwickler sieht in den Subcircuits schnell, welche Komponenten einen Einfluss auf die Ströme und damit auf den Stress haben.

Je nach Art des Betriebs der Baugruppe spielen unterschiedliche Betriebstemperaturen eine Rolle. Daher lässt sich die Stressbelastung der Schaltung für unterschiedliche Temperaturen berechnen und vergleichen. Durch die farbliche Kennzeichnung von gering, mittel bis hin zu stark belasteten Bauteilen bei unterschiedlichen Temperaturen erkennt der Entwickler auf einen Blick, welchen Einfluss Temperaturänderungen auf die diversen Schaltungsteile haben.

Ursachen für Fehler

Die Ursachen für Fehler sind vielfältig. Heute werden viele Schaltungsteile wiederverwendet und die ursprünglich getroffenen Annahmen sind leider zum Teil nicht gut dokumentiert. Wenn sich dann die Versorgungsspannung ändert, müssen auch Bauteilwerte entsprechend angepasst werden. Wenn in Teams an einem Schaltplan gearbeitet wird, werden Abblockkondensatoren für designübergreifende Netze vergessen. Offene beziehungsweise nicht richtig angeschlossene Verbindungen von Leitungen können beim Editieren schnell unabsichtlich entstehen.

Bei Gesprächen mit Elektronikentwicklern hat sich deutlich gezeigt, dass die Ursache für sporadische Fehler einer Baugruppe zu circa 40 Prozent auf Flüchtigkeitsfehler im Schaltplan zurückzuführen ist. Die zweite große Ursache sind undefinierte Zustände in der Software, die die Baugruppe steuert und regelt. Mit den Audits lassen sich die häufigsten Fehler zuverlässig automatisch erkennen und sofort beheben.

Unterstützte Regeln des Audits

Beim Schematic Audit und der Stressanalyse werden über 50 verschiedene Regeln abgeprüft, die sich einzeln ein- und ausschalten sowie konfigurieren lassen. Zu diesen Checks gehören die Checks, die die richtige Verbindung im Schematic prüfen. Es werden beispielsweise nicht komplett angeschlossene (floating) Bauteile, unpassende Bit-Zuweisungen in einem Bus, Input Pins ohne Treiber, Output Pins ohne Empfänger / Last- oder Open-Collector-Schaltungen ohne Pull-Up-Widerstand problemlos erkannt.

Eine weitere Gruppe von Audit-Regeln bezieht sich auf die Bauteile an sich. Beispiele für solche Prüfungen sind, ob der Spannungswert eines Abblockkondensators passt, Werte für generische R, L, C Komponenten zugewiesen sind und ob VoH- und VoL-Werte zugewiesen sind.

In der Gruppe von Protokoll Checks wird geprüft, ob Input Pins mit Pull-Up oder Pull-Down beschaltet sind, die Polarität von differentiellen Paaren passt, die Werte für Pull-Up- oder Pull-Down-Widerstände zu hoch oder zu niedrig sind, Abblockkondensatoren fehlen.

CAD-Flows unterscheiden sich heute hauptsächlich darin, wie viele Prüfungen und Checks unterstützt werden. Die Datenkonsistenz und Einhaltung der Designregeln wie Signalintegrität, Power-Integrität, Fertigung und Bestückung wird jetzt um Syntaxregeln im Schaltplan erweitert. Das frühzeitige Erkennen und Vermeiden von Fehlern hilft Elektronik günstiger und zuverlässiger zu entwickeln.

%20AVILOO.jpg)