Die Digitalisierung in Industrie und privaten Haushalten, der Ausbau der Elektromobilität sowie die wachsende Nachfrage nach nachhaltiger und bezahlbarer Energie und die notwendige Reduktion von CO2-Emissionen sind aktuell beherrschende Themen.

Um diese Herausforderungen zu meistern bedarf es einer effizienten Erzeugung, Steuerung und Nutzung von Energie. Leistungshalbleiter, die hohe elektrische Ströme und Spannungen steuern und schalten, spielen dabei eine wichtige Rolle. Herkömmliche Halbleiter auf Silizium-Basis stoßen hier verstärkt an ihre Grenzen und werden zunehmend von GaN-Halbleitern verdrängt. Diese bieten mehr Leistung auf kleinerem Raum, sparen Energie und minimieren so den CO2-Fußabdruck.

Die speziellen chemisch-physikalischen Materialeigenschaften von GaN-Halbleitern mit großer Bandlücke und der Aufbau von High-Electron-Mobility Transistoren werfen jedoch neue Fragen auf: „Besondere Herausforderungen stellen dabei die hohen elektrischen Feldstärken sowie enormen Strom- und Leistungsdichten mit entsprechend hoher Materialbelastung in diesen sehr kompakten Bauelementen dar“, sagt Frank Altmann, Leiter des Geschäftsfelds „Werkstoffe und Bauelemente der Elektronik“ am Fraunhofer IMWS.

UltimateGaN – Durchführung und Erkenntnise

Im kürzlich abgeschlossenen Forschungsprojekt „UltimateGaN“ hatte sich ein Konsortium aus 26 europäischen Partnern aus Wissenschaft und Industrie unter der Leitung von Infineon Austria die Aufgabe gestellt, die Vorteile der GaN-Technologie entlang der gesamten Wertschöpfungskette, von der Prozessentwicklung über Design, Aufbau- und Verbindungstechnologien bis hin zur integrierten Systemlösung, nutzbar zu machen.

Im Rahmen des Projektes hat das Fraunhofer-Institut für Mikrostruktur von Werkstoffen und Systemen IMWS mit hochauflösenden Analyseverfahren und innovativen Fehlerdiagnostik-Methoden zur Prozessoptimierung und Steigerung der Zuverlässigkeit der GaN-Baulemente beigetragen. „Wir erforschen spezifische kritische Defekte oder GaN-spezifische Degradationsprozesse um neue Fehlermodi möglichst früh erkennen, verstehen und damit vermeiden zu können“, sagt Frank Altmann.

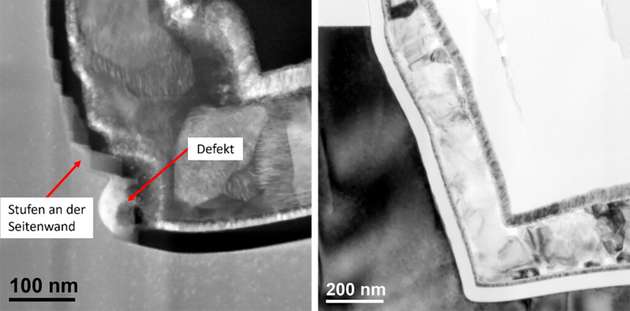

Zum Beispiel wurden nach Zuverlässigkeitstests Leckstrompfade lokalisiert und mikrostrukturell untersucht, um deren Ursache zu ermitteln. So konnte eine neue Defektsignatur identifiziert werden, die zum frühzeitigen elektrischen Durchbruch von speziellen semi-vertikalen GaN-Transistoren führte. Mit den Erkenntnissen konnte der Herstellungsprozess gezielt optimiert werden.

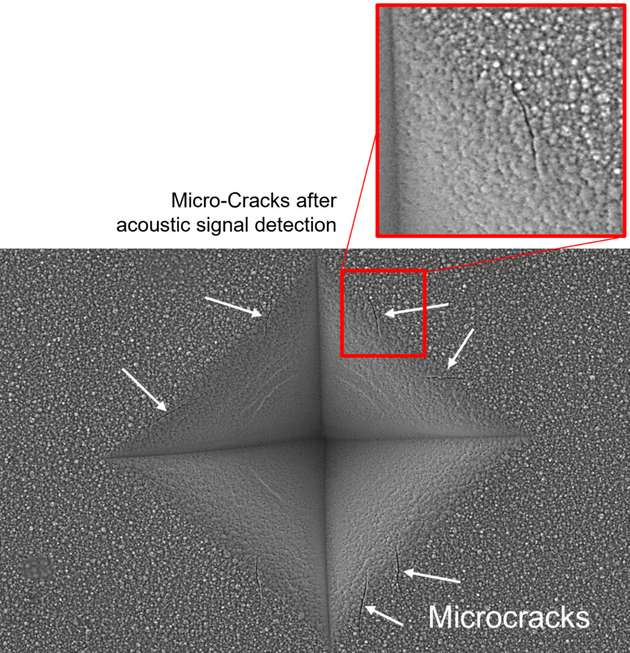

Mit Hilfe von Nanoidentation in Kombination mit Schallemissionsverfahren konnten die Forschenden versteckte Mikrorisse unter den Metallisierungsschichten von Bondpads aufdecken. Dabei wurde die genannte Methodik an den verschiedenen Proben der Projektpartner angewandt und evaluiert und die Defektstruktur mittels elektronenmikroskopischer Analysen untersucht.

Das europäische Projekt „UltimateGaN“ (Research for GaN technologies, devices and applications to address the challenges of the future GaN roadmap) hatte eine Laufzeit von insgesamt dreieinhalb Jahren. Das Projektvolumen von 48 Millionen Euro wurde durch Investitionen der Industrie, Zuschüsse der einzelnen beteiligten Länder und des Europäischen „Joint Undertakings“ ECSEL (Electronic Components and Systems for European Leadership) finanziert.