Laptops, Smartphones oder Smartwatches – im Zuge der voranschreitenden Digitalisierung sollen sie immer mehr Funktionen übernehmen und gleichzeitig kleiner werden. Das geht oft mit einem hohen Energieverbrauch einher. Neue Erkenntnisse der Spinforschung versprechen jetzt, dass sich der Energie- und Flächenverbrauch von elektronischen Geräten deutlich senken lässt, wenn man Spin-Wave-Technologien in Mikrochips verwendet.

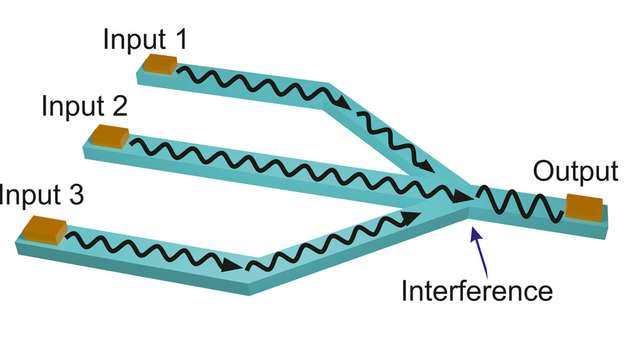

Doch womit beschäftigt sich die Spinforschung überhaupt? Als Spinwellen bezeichnet man die kollektive Anregung in einem magnetischen Material. Ein Spin ist dabei der Eigendrehimpuls eines Quantenteilchens, wie beispielsweise in einem Elektron oder Neutron. Dieser Drehimpuls, also der „Spin“, stellt die Grundlage aller magnetischen Phänomene dar. Die Quantenteilchen der Spinwellen wiederum bezeichnet man auch als Magnonen. Und genau die möchte sich die Spinforschung zu Nutze machen, da sie mehr Informationen transportieren können und weniger Energie verbrauchen als klassische Mikro- und Halbleiterchips.

Fraunhofer IZM auf der Suche nach konkreten Anwendungen

Um diese Konzepte aus der Spin- und Magnonikforschung auf eine konkrete Anwendung zu adaptieren, haben Forschende am Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM zusammen mit europäischen Partnern aus der Forschung und der Industrie ein Rechnersystem konzipiert, bei dem die Magnonik an einen Standardcomputer angeschlossen und somit in gängige Halbleitersysteme integriert wird.

Für eine mögliche Kompatibilität der Technologie hatte das Forschungsteam dabei die so genannte CMOS-Schaltung im Blick. Diese Halbleiterelemente kommen in allen gängigen Rechnern vor und können zugleich digitale als auch analoge Daten speichern und verarbeiten. Im Rahmen des Projekts konzipierte die Gruppe am Fraunhofer IZM einen Chipaufbau für Frequenzen bis circa 16 GHz und mit nahezu gleichlangen Verdrahtungslängen für mehr als 100 Kanäle. Dieser Chipaufbau soll dann die Schnittstelle zwischen einem klassischen PC und einem Spinwellen-Schaltkreis auf Saphir- oder Gadolinium-Gallium-Granat (GGG)-Basis darstellen.

Die besondere Herausforderung dabei stellt die räumliche Dichte der Spinwellen-Logikgatter auf einem Chip dar. Ein Logikgatter bezeichnet einen Rechenoperator, der binäre Eingangssignale zu Ausgangssignalen verarbeitet. „Aktuell wird auf einem dieser Spin-Wellen-Chips nur ein Logikgatter betrieben. Wir wollen künftig über 100 Gatter auf einem Chip platzieren“, erklärt der zuständige Projektleiter am Fraunhofer IZM, Dr. Martin Hempel und blickt dabei zuversichtlich auf die besondere Expertise des Instituts im Bereich der Einbettung von Hochfrequenz-Chips mit vielen Ausgängen.

Forschungsprojekt SPIDER

Im Projekt sollen damit erstmals komplexere Rechenfunktionen eines Computerchips unter Nutzung von Spinwellen demonstriert werden. Damit soll der Weg zu einem 100-fach reduzierten Energieverbrauch von zukünftigen Computersystemen geebnet werden. Weiterhin ermöglicht die vom Fraunhofer IZM in diesem Projekt entwickelte Technologie der Ansteuerung einer Vielzahl von Hochfrequenzkanälen weiterführende Anwendungen auch in anderen Bereichen, wie Hochfrequenz- und Kommunikationssystemen, so zum Beispiel in der Kollisionsvermeidung beim autonomen Fahren.

Das von der Europäischen Union geförderte Horizon-Projekt SPIDER (Spin Wave Computing for Ultimately-Scaled Hybrid Low-Power Electronics) 801055 läuft vom 01. Dezember 2022 bis 31. Mai 2026 und wird mit einer Summe in Höhe von 3 Millionen Euro gefördert. Das Projekt wird vom Interuniversity Microelectronics Centre (IMEC) in Leuven koordiniert. Weitere Projektpartner sind die Technische Universität Delft, die Rheinland-Pfälzische Technische Universität Kaiserslautern-Landau, das nationale Forschungs- und Entwicklungsinstitut für Mikrotechnologien IMT aus Bukarest, sowie die Unternehmen Thales und Akronic.