Automatische Verhaltenssynthese - High-Level-Synthese (HLS) - ist bereits seit Anfang der 80-er Jahre ein akademischer Forschungsbereich. Mit dem Einsatz der HLS-Software wird eine rein funktionale Beschreibung des Designs - ohne Berücksichtigung des Timings - in eine Mikro-Architekturimplementierung auf Register-Transfer-Ebene umgewandelt. Das ursprüngliche Forschungsziel war, die Design- und Verifikationsproduktivität mit Hilfe einer kompakten High-Level-Verhaltensbeschreibung wie C oder MATLAB zu steigern. Allerdings hatten erste Entwicklungswerkzeuge für HLS eine Reihe von Einschränkungen, die das Wachstum und die Größe des HLS-Markts begrenzten. Zu diesen Hindernissen für eine breite Akzeptanz gehörten unter anderem zu viele verschiedene, nicht standardisierte HLS-Beschreibungsformate, fehlende Verifikations- und Design-Methoden auf höherer Abstraktionsebene und auf Datenfluss limitierte Design-Anwendungen, die anfangs der erforderlichen Leistung von dedizierten RTL-Implementierungen gerecht wurden. In den letzten Jahren hat man große Fortschritte gemacht, um alle diese Hürden aus dem Weg zu räumen. Diese Fortschritte haben sich entscheidend auf das Wachstum und die Größe des Marktes für Verhaltenssynthese ausgewirkt.Eines der anfänglichen Hindernisse für eine weitere Verbreitung und Akzeptanz der HLS-Technologie war die fehlende Verfügbarkeit einer standardisierten Hardware-Beschreibungssprache auf einer höheren Abstraktionsebene. Alle früheren angebotenen HLS-Tools arbeiteten mit proprietären Eingabe-Formaten, basierend auf C. Diese angepassten C-Sprachformate beinhalteten oft spezielle Direktiven im Quellcode zur Steuerung der Tools, so genannte Pragmas, die als Anweisungen und Vorgaben für den HLS-Prozess dienten.

SystemC-Standard

Mit der Gründung der Open-SystemC-Initiative (OSCIs) im Juni 2000 wurde die erste Version von SystemC standardisiert, inzwischen ist die Industrie bei Version V2.01 angekommen. Diese C++-Klassen und -Makros bilden eine ereignisgesteuerte Simulationsschnittstelle in C++ und unterstützten eine abstrakte Modellierung von Kanälen, Schnittstellen, Ereignissen und Bibliotheken. SystemC wurde von der IEEE Standards Association als IEEE 1666-2005 und später als IEEE 1666-2011 ratifiziert.Einer der großen Vorteile des Einsatzes von SystemC für HLS ist die Unterstützung der Verifikation. Durch die Verwendung von SystemC steht ein integrierter, ereignisgesteuerter Simulator für die Verifikation zur Verfügung. SystemC unterstützt mehrere komplexe Module, die parallel arbeiten können, erlaubt eine gemeinsame Nutzung von Daten im Speicher und kann die Ausführung mit Hilfe von realen Signal-Protokollen synchronisieren. Mit SystemC kann ein großes System-on-Chip(SoC)-Design in mehrere SoC-IP-Blöcke unterteilt werden, die über Kanäle verbunden sind und einem Standardprotokoll wie ARMs AMBA oder AXI folgen. Diese komplexen Module können dann zusammen verifiziert werden, um die Gesamtfunktion des SoCs sicherzustellen.

Design-Flows

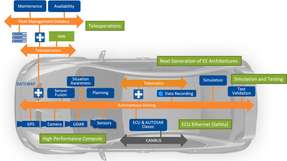

Ein weiteres Hindernis für die Verbreitung von HLS war die fehlende Verfügbarkeit von Entwicklungswerkzeugen und Methoden, welche die Verifikation und Validierung der Verhaltensspezifikation auf höheren Abstraktionsebenen unterstützten. Durch den Einsatz von Design-Methoden wird ein entscheidender Vorteil beim Einsatz von SystemC-basierten Flows, die Transaction-Level-Models (TLM) nutzen, erzielt - eine Steigerung der Produktivität. Obwohl HLS eine zentrale Rolle in dieser Design-Methodik spielt, ist es äußerst wichtig, dass auch ein virtuelles Prototyping, eine RTL-Synthese und ein physikalisches Design unterstützt werden. Aus der Perspektive der Verifikation stellt der virtuelle Prototyp eine frühe Software-Entwicklungsplattform und Testumgebung dar, die bei der Verifikation des Algorithmus und bei Hardware-/Software-Kompromissen hilft. Auf der Ebene der Verhaltenssynthese kann man die Testumgebung weiter verfeinern, zudem sind Abwägungen bezüglich der Architektur im Hinblick auf Timing, Fläche und Leistung möglich. Schließlich führt dies dazu, dass die Testumgebung für die Verifikation der strukturellen Integrität des Designs in RTL und die nachfolgende Erstellung der Netzliste auf Gatterebene für die Platzierung und das Routing verwendet werden kann. Erst wenn alle diese Teile in einer Design-Methodik nahtlos zusammenarbeiten, kann das Design-Team von der vollen Produktivität von HLS profitieren.

Unterschiedliche Anwendungen

Erste HLS-Tools tendierten dazu, sich auf das Design von Datenfluss zu konzentrieren. Diese Arithmetik-lastigen Designs eignen sich für eine Beschreibung in SystemC und ermöglichten durch klare Optimierungs- und Planungsalgorithmen eine entsprechende Design-Leistung für diesen Teil des Gesamt-Designs. Viele dieser Designs wurden in Bildverarbeitungs- und Graphikanwendungen eingesetzt, wo eine High-Level-Beschreibung die beste Möglichkeit bot, eine parallele Anwendung und sich wiederholende Rechenoperationen darzustellen. Dadurch, dass die Produktivität nur im Bereich des Datenflusses des Designs verbessert werden konnte, unterlag die Gesamtproduktivitätssteigerung dem Amdahlschen Gesetz. Weiterhin begrenzten viele der frühen HLS-Tools den Einsatz dieser Datenfluss-Designs nur auf FPGAs und nicht auf ASIC-Designs, um die erforderliche Optimierung zu reduzieren.Heute gibt es SystemC-basierte Tools für die Verhaltenssynthese, die sich problemlos für Designs eignen, die entweder ganz aus Datenfluss, Kontroll-Logik oder einer Kombination aus beiden bestehen. Darüber hinaus berücksichtigen jetzt manche HLS-Tools leistungsfähige Entwicklungswerkzeuge für die Logiksynthese (RTL zu Gatter). Diese ermöglichen nicht nur eine bessere Implementierung der Kontroll-Logik, sondern helfen auch bei der Optimierung des Timings, der Verlustleistung und der Fläche. Damit sind diese Entwicklungswerkzeuge für die Verhaltenssynthese auch in der Lage, bei Timing, Verlustleistung und Fläche mindestens ein gleich gutes oder sogar besseres Ergebnis zu liefern, als mit einem manuell erstellten RTL-Code.

Zukunftsperspektiven

Es hat lange gedauert, bis der HLS-Markt bereit war, aber nun ist die Zeit für die breite Akzeptanz dieser Technologie gekommen. Die Einführung des SystemC-Standards sowie die Verfügbarkeit von Design- und Verifikations-Methoden und Optimierungen der Entwicklungswerkzeuge, die eine Untersuchung der Architektur und eine bessere Qualität von Ergebnissen (bei Timing, Verlustleistung und Fläche) im Vergleich zu dedizierten RTL-Implementationen ermöglichen, hat den Markt für die Verhaltenssynthese fundamental verändert. Die Möglichkeit, vollständige SoC-Designs mit weniger Ressourcen, schneller und mit besseren Ergebnissen zu erstellen, ist jetzt Realität. Die besten Anwender für HLS-Design-Methodiken haben nicht nur Architektur- und Hardware-Kenntnisse, sondern wissen auch, wie Algorithmen- und Architekturkonstrukte in SystemC zu formulieren sind. Sie haben gelernt, wie die Funktionen der Entwicklungswerkzeuge zu nutzen sind, um mit verschiedenen SystemC-Design-Ansätzen die Designs schnell für diese Algorithmen zu optimieren. Dies eröffnet eine völlig neue Epoche der Anwendbarkeit und Wiederverwendung für Designs über SystemC-Bibliotheken, die sich für unterschiedlichste Anwendungen einsetzen lassen. Unabhängig davon, ob ein Design von Datenfluss, Kontroll-Logik oder einer Kombination aus beiden dominiert wird, sollte kein neuer IP-Block entwickelt werden, ohne vorher die Verwendung von Verhaltenssynthese - im Vergleich zu einer dedizierten RTL-Entwicklung - in Betracht zu ziehen.