Ende 2019 hat das technische Subkomitee für COM-HPC der PICMG das Pinout für diese neue High-Performance-Computer-on-Module-Spezifikation verabschiedet. In Kürze wird der Standard offiziell veröffentlicht und erste Module verfügbar.

Systementwickler spezifizieren bereits ihre ersten Carrierboard-Designs und stehen in den Startlöchern, die ersten Leiterplatten zu entflechten, um im Idealfall parallel zu den kommenden Embedded-Server-Prozessoren von Intel und AMD mit eigenen Lösungen auf den Markt kommen zu können. Die hohe Dichte der auf dem Konnektor ausgeführten High-Speed-Schnittstellen stellt Entwickler dabei vor bislang noch nie dagewesene Herausforderungen, die vor allem die Signal-Compliance des Carrierboad-Designs betreffen.

Neueste Interfaces

Die zwei Konnektoren stellen auf ihren jeweils 400 Pins Schnittstellen extrem hohen Taktraten mit bis hin zu 25 Gbit/s zur Verfügung und PCIe Gen 4 und 5. Die neuen PCIe-Generationen verdoppeln für den Performance-Gewinn dabei jeweils die Übertragungsrate. Bietet PCIe Gen 3.0 schon 8 Gigatransfers pro Sekunde (8 GT/s), so verdoppeln sie sich auf 16 GT/S bei PCIe Gen 4 und auf 32 GT/s bei PCIe Gen 5.

Bei den jüngst veröffentlichen Vorab-Details von PCIe Gen 6 ändert sich die Taktfrequenz nicht. Es werden allerdings pro Takt dann 2 statt bisher nur 1 Bit übertragen, indem eine Pulsamplituden-Modulation mit vier Stufen (PAM4) genutzt wird. Vermutlich wird COM-HPC auch diesen Technologiesprung auf PCIe Gen 6 unterstützen können, da der verwendete Stecker eine optimierte Version eines 56-Gbit/s-PAM4-spezifizierten Steckers ist.

Große Herausforderungen kommen

Statistisch sind Entwickler damit auf 12,5 Prozent (1/8 der maximal möglichen Bandbreite von COM-HPC) von dem vorbereitet, was da in Zukunft auf sie zukommt, und mit etwas Abstand betrachtet ist das eine enorme Lernkurve, die sie allein bei PCIe zu bewerkstelligen haben. Sicher, PCIe Gen 6 hängt noch in „weiten Säcken“ und wir noch Jahre brauchen, bis man erste Serienprodukte sehen kann. Aber es reicht auch schon allein der aktuelle Sprung zur nächsten Generation aus. Er bringt beim Wechsel von PCIe 3 auf 4 plus 100 Prozent, von USB 3.2 Gen 2 (das ehemalige USB 3.1 Gen 2 oder SuperSpeed+) auf USB 4.0 (40 Gbit/s) plus 400 Prozent und von 10 auf 25 GbE plus 150 Prozent mehr Performance.

Es ist also auch hier schon leicht zu erkennen, dass man sich gut für die kommenden Herausforderungen rüsten muss. Ein wichtiges Stellglied sind dabei möglichst frühzeitige Compliance-Tests, um eine fehlerfreie Funktion der fertigen Lösung nicht nur auf dem Entflechtungsmonitor, sondern auch im Feld sicherzustellen. Denn selbst wenn bewährte Maßnahmen der HF-Technik, Layoutgestaltung für optimale Signalqualität und Dimensionierungen im Design berücksichtigt werden, können nur umfassende Compliance-Tests kritische Auffälligkeiten schon im Vorfeld zu Tage fördern.

Der Betrieb leicht außerhalb der Compliance kann zu zufälligen, nicht vorhersehbaren Ausfällen führen. Meistens funktioniert das System zwar, aber im praktischen Betrieb mit externen Komponenten können Aussetzer auftreten. Solche sporadisch auftretenden Fehler lassen sich nur sehr schwer analysieren. Dennoch sind sie äußerst kritisch und ihre Folgen werden erfahrungsgemäß teuer. Neben den EMV-Compliance-Tests, die sicherstellen, dass Abstrahlungen definierte Strahlungswerte nicht überschreiten, müssen auch die Transmitter und Receiver der High-Speed-Kommunikationsschnittstellen eine definierte Signalqualität einhalten.

Compliance ermitteln

Betrachtet man beispielsweise PCIe-Schnittstellen, dann garantiert die Einhaltung der PCIe-Spezifikation die erfolgreiche Kommunikation zwischen dem Mainboard und jeder beliebigen Peripheriekomponente. Vorausgesetzt, beide Seiten sind „compliant“ und halten die Spezifikation ein. Befinden sich die Werte zwar außerhalb, jedoch in Grenznähe, kann die Kommunikation des Boards mit den Devices zwar funktionieren. Es kann im realen Einsatz allerdings zu Übertragungsfehlern kommen.

Ein erkannter Fehler in der Kommunikation löst zudem eine erneute Übertragung des Datenpaketes aus. In der Folge sinkt die tatsächlich erreichte Datentransferrate. Eine im Labor erfolgreich getestete Kommunikation ist damit also noch lange kein Nachweis der Compliance. Der Nachweis der Compliance kann nur durch eine ausführliche Charakterisierung des Designs mittels präziser Messungen geführt werden.

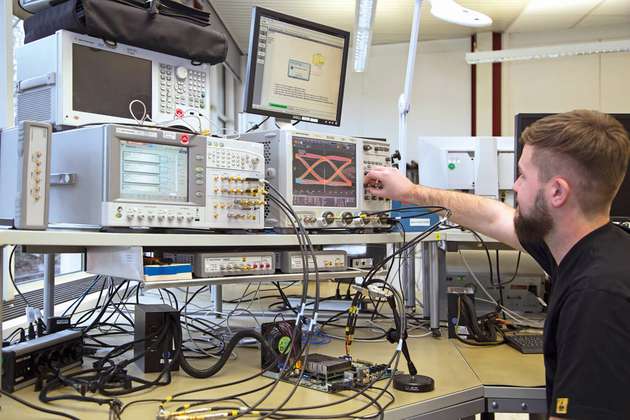

Hierfür betreiben Computer-on-Modules-Spezialisten wie Congatec eigene Testlabors, die mit teuren Präzisionsmessgeräten ausgestattet sind. Der Vorteil eines hausinternen Labors liegt dabei auf der Hand: Je tiefer man in der sicheren Zone arbeitet, umso höher ist die Zuverlässigkeit und Funktion über lange Zeit. Eine genaue Kenntnis der Sicherheitsmarge trägt zur Qualitätssicherung und auch -steigerung bei.

Optimiert werden die Produkte zuerst mittels Simulationen. Verifiziert werden kann die Optimierung jedoch nur mittels umfangreicher Empfänger- (RX) und Sender- (TX) Compliance-Messungen. Um die Zukunftssicherheit für High-Speed-Interfaces, wie sie COM-HPC bietet, zu gewährleisten, wurde bei Congatec bereits in 2018 auch ein neuer Messplatz angeschafft, der die Charakterisierung der kommenden „Next Generation“-Transmitter und -Receiver – einschließlich PCIe Gen 5.0 und USB 4.0 und weit darüber hinaus – erlaubt. Auch im Bereich „Signal Integrity“ kann das Unternehmen auf ausgewiesene Spezialisten zurückgreifen, um umfassende Services anbieten zu können.

Mehr Wärmeleistung abführen

Hinsichtlich der Compliance gerät auch thermische Belastung zunehmend ins Blickfeld dieser Embedded-Designs, da thermische und elektrische Eigenschaften interagieren. Sie bringen schon heute physikalische Kausalketten zum Vorschein, die bei Low-Power-Produkten, wie sie im klassischen Embedded-Computing-Markt bislang üblich sind, nicht gravierend in Erscheinung treten.

Bei COM-HPC-Server-Modulen werden jedoch bis zu 300 W Leistung über die Konnektoren geführt. Für COM-HPC-Client-Module sind bis zu 200 W spezifiziert. Damit werden konforme Designs sowohl der Module als auch des applikationsspezifischen Carrierboards nochmals deutlich komplexer.

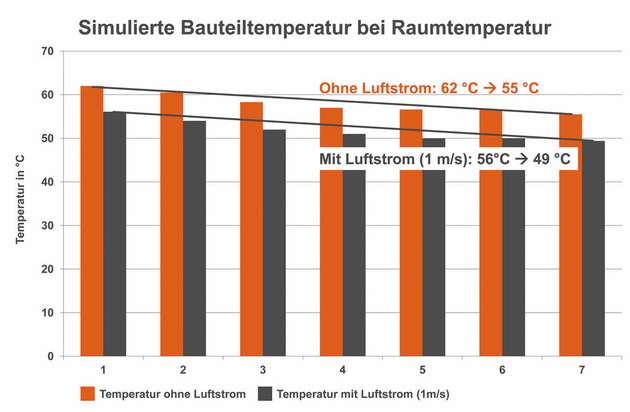

Hierbei ist nicht nur die Entwärmung der CPU, sondern aller Halbleiter- und Leistungselemente zu optimieren. Eine gute thermische Anbindung bedeutet in der Regel auch eine gute elektrische Anbindung für eventuelle Störsignale auf Signalleitungen. Um diese zu optimieren, empfehlen sich zwei Arten der thermischen Simulation: zum einen die rein thermische Betrachtung. Sie stellt ausschließlich das Element und die Verlustleistung der Bauteile in den Fokus. Zum anderen die elektrothermische Simulation. Sie berücksichtigt darüber hinaus auch den Strom auf der Leiterbahn – speziell in den Stromversorgungen. Ihre Wärme wird über Vias auf die großen Kupferflächen einer GND-Plane abgeleitet.

Zu berücksichtigen ist deshalb auch der Einfluss dieser Vias und ihrer Lage im Design. Die Erwärmung der Leiterbahnen bedingt aber auch eine Widerstandsänderung in den benachbarten Signalleitungen. Diese Impedanzverschiebung hat wiederum Einfluss auf die Signalqualität. Signal Integrity ist also ein Thema, das sich bis hin zur Optimierung des Entwärmungskonzepts auswirkt.

Compliance mit Brief und Siegel

Das Ziel ist letztlich, den Nachweis zu erbringen, dass Kunden das Ziel der Compliance sicher erreichen und das auch durch ein Messprotokoll zu bestätigen. Zum Compliance-Test muss idealerweise die komplette Einheit, bestehend aus dem Computer-on-Module und passendem Carrierboard, geprüft werden.

Damit der Kunde später seinen eigenen Compliance-Test erfolgreich bestehen kann, schöpft Congatec auf der eigenen Seite alle technischen Möglichkeiten aus. Im hauseigenen, speziell dafür ausgestatteten Testlabor muss ein COM-HPC-Modul in Funktionseinheit mit einem Congatec-Referenz-Carrier in einem „Pre-Compliance“-Test seine Compliance-Fähigkeit unter Beweis stellen. Solche Tests für Transmit und Receive zum Standard bei seinen Produkt zu machen, belegen den hohen Qualitätsanspruch des Computer-on-Modules-Spezialisten.

Die gleichen Compliance-Tests bietet das Unternehmen Kunden auch für COM-HPC-basierte Carrierboard-Modul-Kombinationen an. Kunden sparen so Investitionen in eigene oder externe Labors und profitieren vom Expertenwissen des Computer-on-Modules-Experten, was auch die Findung eines Ansprechpartners für die Problemlösung im Falle einer Incompliance des Carrierboards besonders einfach macht.

-congatec%20upgrades%20its%20Server.jpg)