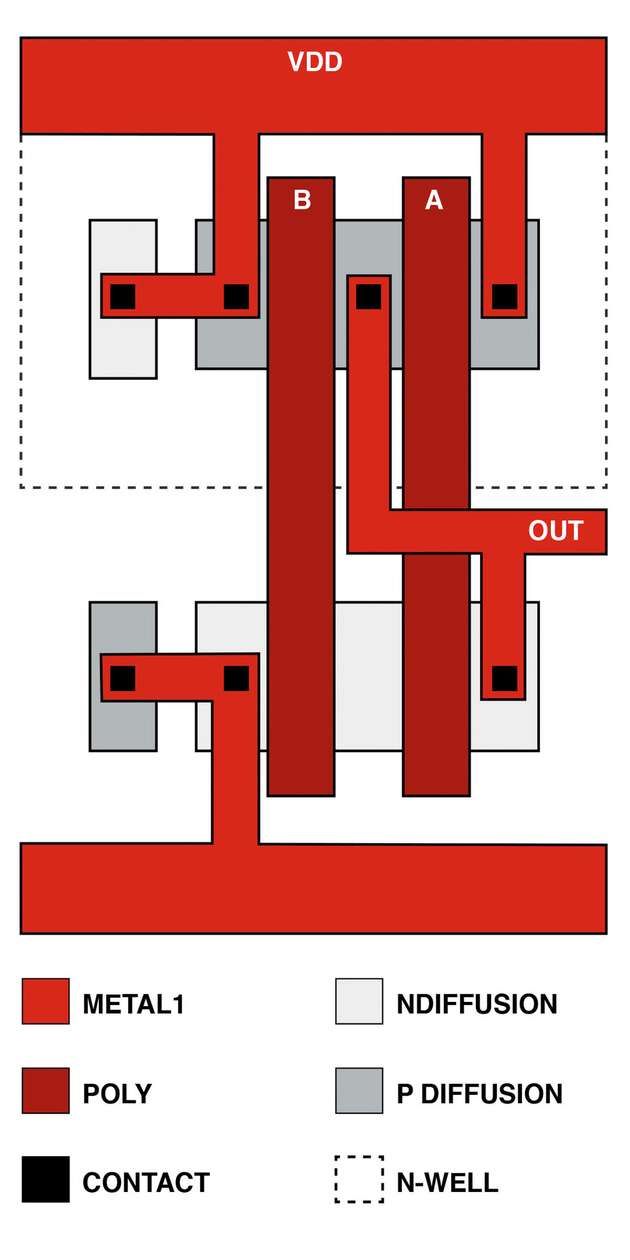

Seit der Erfindung des CMOS-Prozesses (Complementary Metal Oxide Semiconductor) 1963 ist es der Elektronikindustrie gelungen, die Gate-Geometrien auf weniger als 45 nm zu reduzieren. Große System-on-Chip-Bausteine (SoCs) sind inzwischen zur Massenware geworden, und zusätzlich werden FPGAs, ASICs und Prozessoren mit extrem hoher Schaltungsdichte auf dem Markt angeboten. Abbildung 1 zeigt ein mit CMOS-Technologie implementiertes NAND-Gatter.

Parallel dazu haben auch leistungsfähige BiCMOS-Prozesse auf der Basis von Silizium-Germanium (SiGe) allgemeine Verbreitung erlangt. Sie ermöglichen es, extrem schnelle Schaltungen für Hochfrequenz- und Computeranwendungen herzustellen, in denen CMOS-Bauelemente für Logikfunktionen genutzt werden. Diese Prozesse sind sehr schnell: die fT-Werte von Bipolartransistoren erreichen mehr als 50 GHz und liegen in Einzelfällen sogar über 200 GHz. Da diese Prozesse auch CMOS-Module enthalten, lassen sich auch Logikfunktionen und Zustandsautomaten hoher Dichte integrieren. Welcher Prozess eignet sich also am besten zum Treiben von Übertragungsleitungen mit hohen Frequenzen?

CMOS-Schaltungsdichte und DGO

Die CMOS-Prozesstechnologie dominiert heute die Elektronikwelt. Im gesamten Spektrum vom Mobiltelefon bis zu riesigen Serverfarmen wird sie für den Großteil der hochleistungsfähigen und (relativ) wenig Leistung aufnehmenden Anwendungen mit ihren zahlreichen Transistoren eingesetzt. Damit dies möglich ist, haben die Prozessingenieure die Kanallänge der FETs immer weiter reduziert. Für diese Länge gibt es zwei Maße: die gezeichnete und die effektive Länge. Die gezeichnete Länge ist das dem Entwurf entsprechende Maß des leitenden Kanals zwischen der Source und der Drain des Transistors. Beim Implantieren von Drain und Source wird die Kristallstruktur des Substrats jedoch beschädigt, sodass der Wafer anschließend geglüht werden muss, um die Kristalldefekte zu reparieren. Während dieses Prozesses diffundieren die Source- und Drain-Zonen, sodass sich die Kanallänge auf den effektiven Wert reduziert.

Die Funktion von FETs beruht darauf, dass durch Anlegen eines elektrischen Felds Majoritätsladungsträger in den leitenden Kanal zwischen Source und Drain gezogen werden. Hierzu isoliert man den Kanal mithilfe einer extrem dünnen Oxidschicht, auf die ein leitendes Gatematerial aufgebracht wird (deshalb die Bezeichnung Metal Oxide Semiconductor, auch wenn anstelle des Metalls inzwischen Polysilizium verwendet wird). In der Vergangenheit wurde die isolierende Oxidschicht hergestellt, indem man das Silizium zu SiO2 oxidierte. Wegen der geringeren Gatterlänge muss die von der Dielektrizitätskonstante des Oxids abhängige, elektrische Dicke der Oxidschicht ausreichend gering sein, damit man ein elektrisches Feld mit der richtigen Stärke erhält. Bei modernen Prozessen mit extrem kleinen Geometrien verwendet man Oxide des Elements Hafnium, dessen Dielektrizitätskonstante wesentlich höher ist. Um dieselbe elektrische Dicke zu erzielen, wäre eine Schicht aus SiO2 einfach zu dünn. Elektronen würden sie einfach durchtunneln und damit den Isolator effektiv ignorieren.

Vor- und Nachteile von dünn

Wenn es um das Treiben hochfrequenter Signale geht, hat die dünnere Oxidschicht sowohl Vorteile als auch Nachteile. Zunächst ist es wegen des elektrisch dünneren Oxids möglich, die Feldstärke durch Absenken der Versorgungsspannung zu reduzieren, ohne dass sich die Leistungsfähigkeit verschlechtert. Die Verlustleistung von CMOS-Schaltungen ist eine Funktion der Frequenz (f), der Aktivität α (Schalthäufigkeit), der parasitären Kapazität C der Gates und Verbindungsleitungen) und der Versorgungsspannung V sowie des Leckstroms ILEAK :

PCMOS = αfCV2 + iLEAKV (Gleichung 1)

Wie man sieht, ist die Verlustleistung eine Funktion des Quadrats der Versorgungsspannung. Auch ein geringfügiges Reduzieren der Betriebsspannung von beispielsweise 2 auf 1,8 V verringert die Verlustleistung somit entscheidend (in diesem Fall um 19 Prozent, wenn man die Leckverlustleistung außer Acht lässt). Man kann sich vorstellen, wie sich dies bei einem Baustein mit Milliarden von Transistoren auswirkt. Nachteilig ist eine dünnere Oxidschicht dagegen in den I/O-Stufen der Bauelemente. Wegen der geringen Spannungsfestigkeit von Transistoren mit geringer Oxidstärke wendet man deshalb für die I/O-Schaltungen einen abgewandelten Prozess an, sodass also zwei verschiedene Oxiddicken zum Einsatz kommen. Mit dieser DGO-Technik (Dual Gate Oxide) kann man Transistoren mit höherer Spannungsfestigkeit herstellen. Die Tatsache, dass dies jedoch nur in gewissen Grenzen möglich ist, begrenzt die Einspeise-Amplitude von schnellen Signalen.

Deutlich wird dieses Phänomen bei modernen High-Density-FPGAs und -ASICs. Die Geschwindigkeit der I/O-Abschnitte wurde hier von früher 1 bis 2,5 GBit/s auf über 10 GBit/s angehoben. Dafür aber ging die Signalamplitude zurück, was wiederum unmittelbare Auswirkungen auf den Signal-Rauschabstand (Signal-to-Noise Ratio, SNR) hat. Je geringer der SNR wird, umso mehr steigt die Bitfehlerrate. In einigen Fällen sind zusätzliche externe Schaltungen erforderlich, um das Signal zur Reduzierung dieser Fehler aufzubereiten. Wenn die Übertragungsraten von 10 GBit/s auf 25 GBit/s und mehr angehoben werden, wird man CMOS-Schnittstellen aus den beschriebenen Gründen nur über kurze Distanzen zum Treiben von Leitungen einsetzen können.

Pluspunkte von BiCMOS

Bipolare SiGe-Schaltungen kombiniert mit CMOS- oder BiCMOS-Prozessen beinhalten mehr Prozessschritte als traditionelle Bulk-CMOS-Schaltungen. Außerdem sind BiCMOS-Prozesse teurer in der Herstellung. Durch das Hinzufügen leistungsfähiger Bipolartransistoren kommt der Prozess jedoch auch für sehr spezielle Anwendungen in Frage wie etwa Kfz-Radarsysteme, UHF-Funksysteme und Signalaufbereitungs-Schaltungen. Der Großteil der Aufbereitung von Datensignalen erfordert Logik, wenn auch in den meisten Fällen nur in minimalem Umfang. Dagegen ist der Logikaufwand bei anspruchsvolleren Signalaufbereitungs-Funktionen wie Re-Timern oder DFE-Blöcken (Decision Feedback Equalization) erheblich größer. Wäre man nicht in der Lage, Bipolartransistoren für geringes Rauschen und höhere Treiberspannungen mit der hohen Dichte von CMOS-Schaltungen zu kombinieren, könnte man Bauelemente dieser Art nicht herstellen. Die Kombination aus SiGe und CMOS bietet beide Qualitäten: CMOS sorgt für hohe Logikdichte, während die SiGe-Bipolartransistoren für die Treibereigenschaften und die Spannungsfestigkeit genutzt werden.

Bipolartransistoren im Signalkanal einzusetzen, bietet zwei Vorteile: Erstens ist eine höhere Einspeise-Amplitude möglich, wodurch sich der SNR verbessern kann. Zweitens lässt sich geringeres Rauschen mit höherer Verstärkung kombinieren, was ebenfalls den SNR verbessert. Die für die anspruchsvollen Signalaufbereitungs-Stufen erforderlichen Logik- und DSP-Funktionen lassen sich problemlos mit der CMOS-Komponente des Prozesses produzieren. Möglicherweise ist die Kombi-Lösung teurer, aber die Leistungsfähigkeit ist höher als bei einer reinen CMOS-Implementierung.

Fazit

Wenn möglichst wenig Verlustleistung und ein Maximum an Transistordichte gefragt sind, ist CMOS der Prozess der Wahl. Mit Prozesspunkten unter 45 nm werden routinemäßig große SoC-Bausteine entwickelt. Diese können mehrere Prozessorkerne, Signalprozessoren und sogar Funk-Schaltungen enthalten – alles in einem Baustein kombiniert. Geht es aber um die schnelle Datenübertragung mit erhöhten Übertragungsraten, so geraten reine CMOS-Schaltungen wegen der mangelnden Einspeise-Amplitude und des reduzierten SNR gegenüber den SiGe-BiCMOS-Prozessen ins Hintertreffen. Beide Technologien können jedoch durchaus in einem System koexistieren. Wenn es wegen der CMOS-typischen Einschränkungen in einem FPGA, ASIC oder Prozessor zu Signalintegritäts-Problemen mit einem High-Speed-Interface (z. B. PCIe 3.0 mit 8 GBit/s) kommt, bietet ein Signalaufbereitungs-Teil auf BiCMOS-Basis die Möglichkeit, das Signal zu regenerieren und mit höherer Amplitude wieder auszugeben. Hierdurch verbessert sich der Gesamt-SNR. Sobald die CMOS-Technologie also an ihre Grenzen stößt, gibt es Lösungen, um die Beeinträchtigung der Signalintegrität zu beheben.