Die Grundidee ist einfach: Während in der Vergangenheit auf Transistoren ausschließlich gerechnet wurde, übernehmen sie nun die Speicherung der Daten gleich mit. Das spart Zeit und Energie. „Und es erhöht so die Leistungsfähigkeit der Chips“, sagt Hussam Amrouch. Die Transistoren, auf denen der Professor für AI Processor Design der Technischen Universität München (TUM) sowohl rechnet als auch Daten speichert, sind gerade einmal 28 Nanometer groß, und millionenfach in neuen KI-Chips verbaut.

Die Chips der Zukunft müssen schneller und effizienter sein und dürfen sich nicht so schnell erhitzen wie bisher: Nur dann sind etwa Berechnungen in Echtzeit während des Flugs einer Drohne möglich. „Derartige Aufgaben sind für einen Rechner extrem komplex und energieintensiv“, erläutert der Professor.

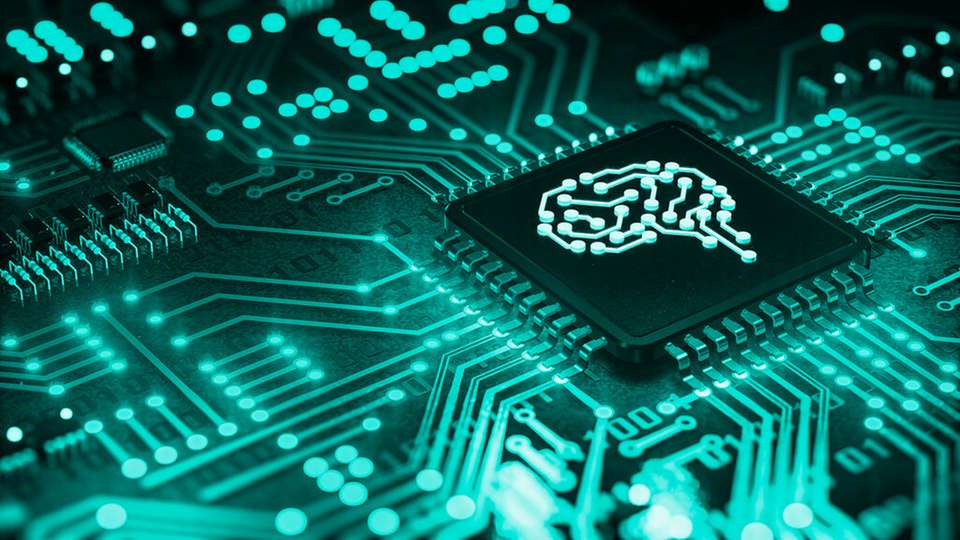

Moderne Chips: Viele Arbeitsschritte, wenig Energie

Mathematisch fassen lassen sich diese wichtigsten Anforderungen an einen Computerchip in „TOPS/W“. Das ist gewissermaßen die Währung für die Chips der Zukunft. Die Frage ist, wie viele Trillionen (T) Arbeitsschritte (englisch: Operations, OP) pro Sekunde (S) ein Prozessor ausführen kann, wenn er eine Energie von einem Watt zur Verfügung hat. 885 TOPS/W schafft der neue KI-Chip, der in einer Forschungskollaboration mit Bosch und Fraunhofer IMPS entwickelt und vom US-Unternehmen GlobalFoundries in der Fertigung unterstützt wurde.

Er ist damit mehr als doppelt so leistungsfähig wie vergleichbare KI-Chips, darunter ein „MRAM“-Chip von Samsung. Aktuell oft eingesetzte so genannte CMOS-Chips liegen bei zehn bis 20 TOPS/W. Das zeigen gerade veröffentlichte Ergebnisse in der Fachzeitschrift Nature.

In-Memory-Computing funktioniert wie das Gehirn des Menschen

Das Prinzip der modernen Chiparchitektur haben sich die Forschenden vom Menschen abgeschaut. „Im Gehirn übernehmen die Neuronen die Verarbeitung von Signalen, während die Synapsen in der Lage sind, sich diese Informationen zu merken“, erläutert Amrouch die Fähigkeit des Menschen, zu lernen und sich komplexe Zusammenhänge merken zu können. Der Chip nutzt dafür „ferroelektrische“ Transistoren (kurz FeFET) – elektronische Schalter, die zusätzlich spezielle Eigenschaften (Umpolung bei Anlegen einer Spannung) mitbringen und selbst dann Informationen speichern können, wenn sie vom Strom getrennt werden.

Zudem garantieren sie die gleichzeitige Speicherung und Verarbeitung von Daten innerhalb der Transistoren. „Jetzt können wir sehr effiziente Chipsätze bauen, die etwa für Deep-Learning-Anwendungen, in der generativen KI oder der Robotik eingesetzt werden können, etwa dort, wo Daten direkt am Ort ihres Entstehens verarbeitet werden müssen“, ist Amrouch überzeugt.

Marktreife der Chips erfordert interdisziplinäre Zusammenarbeit

Das Ziel ist, den Chip für die Berechnung von Deep-Learning-Algorithmen, für die Erkennung von Gegenständen im Raum oder ohne jegliche Verzögerung von Drohnen im Flug einzusetzen. Bis es so weit ist werden nach Ansicht des Professors aus dem integrierten Forschungsinstitut Munich Institute of Robotics and Machine Intelligence (MIRMI) der TUM jedoch noch einige Jahre vergehen. Mit dem ersten praxistauglichen In-Memory-Chip rechnet der Wissenschaftler in frühestens drei bis fünf Jahren.

Der Grund dafür liegt unter anderem in den Sicherheitsanforderungen der Industrie. Um etwa eine entsprechende Technologie in der Automobilindustrie einsetzen zu können, muss sie nicht nur zuverlässig sein, sondern auch den individuellen Kriterien in der jeweiligen Branche genügen. „Das zeigt einmal mehr, wie wichtig es ist, dass Forschende aus unterschiedlichen Disziplinen wie Computerwissenschaft, Informatik und Elektrotechnik interdisziplinär zusammenarbeiten“, sagt Hardwareexperte Amrouch, der darin eine besondere Stärke des MIRMI sieht.