Die zunehmende Komplexität von Hardware und Software stellt Chipentwickler vor ständig steigende Verifikationsanforderungen. Um die eng getakteten Projektpläne der Hersteller einhalten zu können, müssen die Entwickler die vier Kernwerkzeuge formale Verifikation, Simulation, Emulation und FPGA-basiertes Prototyping bestmöglich aufeinander abstimmen.

Zu Beginn, wenn Designblöcke (IP) und Teilsysteme entwickelt werden, stehen die formale Verifikation und die Simulation im Vordergrund. Im weiteren Verlauf kommen dann durch Hardware unterstütze Technologien wie Emulationen oder

FPGA-basierte Prototypen zum Einsatz. Im Vergleich zu Emulationen werden FPGA-basierte Prototypen für die Entwicklung von Software mit höherer Geschwindigkeit eingesetzt. Im Gegenzug bieten Emulationen einen besseren Einblick in die Hardware als FPGA-basierte Prototypen.

Hohe Anforderungen an Prototypen

Mehr als 80 Prozent aller Designs werden in FPGA-basierten Prototypen ausgeführt. Der Aufwand und die Kosten für die Abbildung des Designs in einer FPGA-Architektur sind jedoch sehr hoch. Zu den wichtigsten Herausforderungen gehören:

die Re-Modellierung und Abbildung von ASIC-Speichern mit knappen FPGA-Ressourcen,

die Synchronisierung von Design-Clocks für mehrere ASIC-Bereiche auf der Leiterplatte und in den FPGAs,

die Partitionierung des Designs in mehrere FPGAs, falls ein einzelner FPGA nicht ausreicht

und die Verifikation, ob das Design nach allen Modifikation funktional noch identisch zum Originaldesign ist.

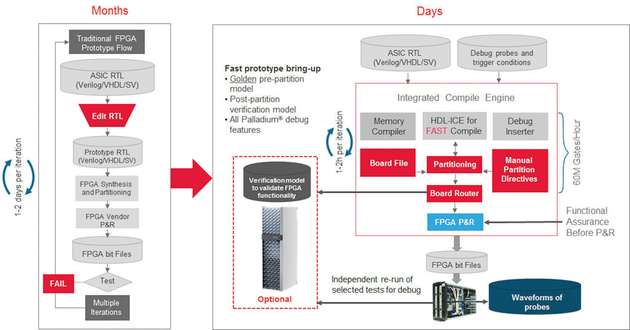

Unter Berücksichtigung all dieser Faktoren kann es einige Monate dauern, bis der Prototyp korrekt funktioniert und bereit für die Übergabe an die Softwareentwickler ist (Time-to-Prototype). Durch schnellere Simulationen und frühzeitiger zur Verfügung stehende FPGA-basierte Prototypen ließe sich nicht nur die Zeit bis zum Tape-Out, als der Abgabe bei der Fertigung, beschleunigen, sondern es wäre auch schon früher möglich, parallel eine Software auf den FPGA-basierten Prototypen zu entwickeln.

Als Teil seiner Verifications-Suite hat Cadence neue Entwicklungswerkzeuge für Simulationen und für FPGA-basiertes Prototyping vorgestellt. Xcelium ist das branchenweit erste Simulationswerkzeug der dritten Generation. Es kombiniert eine Multi-Core-Engine, die für die Simulation von System-on-Chips (SoC) ausgelegt ist, mit einer Single-Core-Engine für schnelle IP-Simulationen. Die Multi-Core-Lösung analysiert das Design automatisch und wählt die passende Konfiguration für die Geschwindigkeit. Im Durchschnitt beschleunigt sich die Simulation für RTL (Register Transfer Level) dadurch um das Dreifache, für Gate-Levels um das Fünffache und für Design-for-Tests um das Zehnfache. Die Single-Core-Engine liefert im Vergleich zum bisherigen Cadence-Simulator „Incisive Enterprise“ ein durchschnittlich doppelt so schnelles Ergebnis.

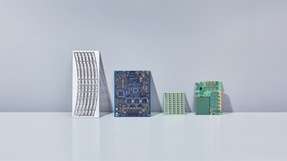

Das Tool Protium S1 steht dem Nutzer gemeinsam mit dem Emulationwerkzeug Palladium Z1 zur Verfügung. Dadurch ist die Einheitlichkeit des Designs gewährleistet, und die Verifikationsumgebungen der Emulation lassen sich wiederverwenden. In Protium S1 kann die Geschwindigkeit eines Designs von 3 bis 100 MHz skaliert werden. Die Implementierung erfolgt wahlweise vollautomatisch oder manuell. Für das Softwaredebugging stehen dem Entwickler hilfreiche Funktionen zur Verfügung, beispielsweise der Up- und Download von Speichern, spezifische Signalsetzungen und eine auf dem Standard SCE-MI basierende Transaktionsschnittstelle.

Mit Hilfe von Protium S1 lässt sich die Time-to-Prototype von Monaten auf wenige Wochen oder sogar Tage reduzieren. Der Schlüssel zur verkürzten Time-to-Prototype ist der Multi-Fabric-Compiler. Traditionelle FPGA-basierte Prototypen erfordern erhebliche Modifikationen des RTL, da das Design in den FPGA-Strukturen abgebildet oder teilweise über mehrere FPGAs hinweg partitioniert werden muss. Im Anschluss folgen die FPGA-

Synthese und das Place&Route (P&R) des FPGAs. Jeder dieser Schritte kann mehrere Tage dauern. Die am RTL vorgenommenen Modifikationen machen eine funktionale Verifikation schwierig, zumal der Einblick in die FPGA-basierten Strukturen für das Debugging beschränkter ist als bei einer auf Prozessoren basierenden Emulation.

Im Gegensatz dazu verwendet Protium S1 dasselbe Frontend wie die Emulation. Chipdesigner brauchen die RTL nicht extra zu modifizieren. Das Design wird automatisch partitioniert. Die ASIC-Speicher werden unter Verwendung einer umfangreichen Modellbibliothek automatisch kompiliert. Die verschiedenen Takte des Designs werden vollautomatisch mit einem Mastertakt synchronisiert. Auch das P&R des FPGAs ist voll integriert. Vor der zeitraubenden Ausführung dieses Schritts kann der Nutzer die Partitionierung manuell beeinflussen und alle bewährten Debugging-Tools von Palladium Z1 verwenden, um die Funktionalität des Designs zu verifizieren. Zusätzlich kann er die Informationen des Frontends an das P&R weiterleiten, was eine weitere Verbesserung der Partitionierung und des Layouts zur Folge hat. Im Vergleich zu traditionellen Ansätzen ist der Prototyp viel früher verfügbar und speziell für Softwareentwickler ausgelegt.

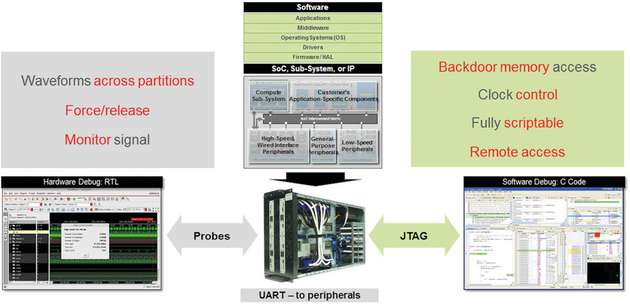

Verbessertes Hard- und Softwaredebugging

Nachdem ein SoC inklusive seiner Software in Protium S1 abgebildet wurde, können die Hardware und die Software analysiert und getestet werden. Das Hardwaredebugging ist etwas begrenzter als bei der Emulation, die dem Benutzer über einen bestimmten Zeitraum hinweg alle Signale im Design zuverlässig aufzeigt. Für FPGA-basierte Prototypen können Wellenformen der Hardware aber nicht nur pro FPGA, sondern auch pro Design über mehrere FPGAs hinweg angezeigt werden. Der Anwender kann ausgewählte Signale überwachen. Vor der Kompilierung entscheidet er, welche Signale er detailliert mit Hilfe von Probes untersuchen möchte. Außerdem kann er während der Ausführung Signale verändern, was vielfältige Analysen ermöglicht.

Klassisches Softwaredebugging erfolgt über eine JTAG-Schnittstelle, genauso wie beim echten Chip und der Leiterplatte, sobald diese zur Verfügung stehen. Im Vergleich dazu bieten die Debugging-Tools von Protium S1 mehr Flexibilität, zum Beispiel in Form von Scripting, direkter Taktsteuerung oder Start und Stopp während der Laufzeit. Auch Backdoor-Zugriffe auf ASIC Speicher, mit deren Hilfe neue Tests oder aktualisierte Softwareversionen geladen werden können, sind in Protium S1 möglich. Das engere Zusammenrücken von Emulation und Prototyping verkürzt die Time-to-Prototype erheblich.

-no-template-german.jpg)