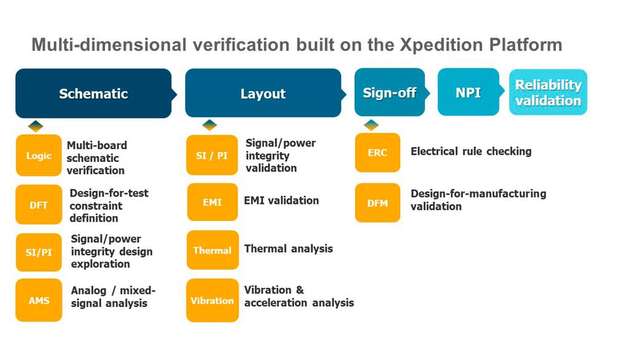

Mit der zunehmenden Komplexität heutiger Systeme stehen Leiterplattendesign-Manager mangels robuster Verifikations-Tools und/oder aufgrund von Schwierigkeiten bei der Anwendung dieser Tools vor der Herausforderung, Probleme frühzeitig in der Design-Entwicklungsphase zu erkennen. Mentor hat vor Kurzem die Xpedition-Leiterplattendesign-Plattform für die mehrdimensionale Verifikation angekündigt, die Ingenieuren diese Aufgaben erleichtern soll.

Probleme leichter erkennen

Mit den Mentor-Tools sollen Ingenieure innerhalb einer einzigen Authoring-Umgebung eine breite Palette an Verifikations-Tools in eine Leiterplatten-Designplattform integrieren können. Dadurch werden Probleme in der Schaltplan- oder Layout-Phase leichter erkannt.

Daneben bietet Xpedition für nicht spezialisierte Mainstream-Leiterplatteningenieure simultane Designanalyse und -verifikation sowie umfassende Tool-Integration. Damit lassen sich laut Hersteller erhebliche Zeit- und Kosteneinsparungen bei gleichzeitiger Bereitstellung hochwertiger Produkte erzielen.

Studie zeigt teure Respins auf

Laut einer Studie von Lifecycle Insights vom 13. September 2018 im Bereich der Elektroniksimulation beträgt die durchschnittliche Anzahl der Design-Respins 2,9 pro Projekt. Dies entspricht 16 Tagen ungeplanter Entwicklungszeit bis zur Fertigstellung eines jeden Respins. Die zusätzlichen Kosten hierfür belaufen sich auf mehr als 82.600 US-Dollar.

In der Studie wurde auch festgestellt, dass Leiterplatten-Designteams, die eine Shift-Left-Verifikationsmethode in ihren Designprozessen verwendeten, eine 14-prozentige Steigerung bei der termingerechten Projektabwicklung, weniger Respins und eine insgesamt bessere Designqualität erzielten.

„Unsere jüngste Forschung zeigt, dass der breite Einsatz von Analyse und Verifikation während der gesamten Designphase unmittelbar die Bemühungen des Engineering-Managements unterstützt, den Designzyklus zu verkürzen und gleichzeitig die Qualität der Baugruppensysteme zu verbessern“, sagt Chad Jackson, Präsident und Chefanalyst von Lifecycle Insights. „Mentors Fortschritte bei Simulationslösungen für Leiterplattendesigns sind für solche Bemühungen ein entscheidender Faktor, und Manager sollten sich diese Angebote genau ansehen.“

Analyse für Mainstream-Designer

Mentors Verifikationsplattform nutzt Best-Practice-Prozesse. Nicht spezialisierte Mainstream-Leiterplattendesigner sollen damit schnell und intuitiv Simulations- und Analysefunktionen erlangen. Integrierte Verifikationstechnologien, die innerhalb des Authoring-Tools des Designers eingeführt wurden, ermöglichen automatische Modellerstellung, gleichzeitige Simulation, Cross-Probing aus Ergebnissen und Fehlerüberprüfungen in einer einzigen Umgebung.

Hinzu kommen weitere Technologien: Schaltplananalyse, Signal-Integritäts(SI)- und Power-Integritäts(PI)-Analyse, Überprüfung der elektrischen Regeln (ERC), thermische Simulation, Schwingungsanalyse, Design-for-Fab (DFF), -Assembly (DFA) und -Test (DFT) sowie Prüfung der Herstellbarkeit. Diese integrierten Technologien, die in einer einzigen, dem Designer vertrauten Authoring-Umgebung zum Einsatz kommen, ermöglichen die frühe Erstellung von virtuellen Designprototypen.

Integrierte Technologien der Design-Plattform

Außerdem enthält Xpedition nach Herstellerangaben folgende, neuartige Technologien:

Verifizierung des Schaltplanentwurfs: Ein vollautomatisches Tool zur Integritätsprüfung von Schaltplänen ersetzt die manuelle visuelle Schaltplanprüfung und reduziert Respins in einem frühen Designstadium um bis zu 70 Prozent.

Design-for-Test-Analyse: Identifiziert die Testpunktanforderungen. Diese werden als Bedingungen automatisch vom Schaltplan an das Layout übergeben und sollen dadurch die Testbarkeit verbessern. Die Funktion erzeugt Test- und Inspektionsdaten für Maschinen in der Prozessvorbereitung mit frühzeitiger Diagnose, was die Gesamtkosten der Prüfung senken kann.

Dabei gehören zu den verbesserten Integrationen in der neuen Xpedition-Plattform:

Design-for-Manufacturability(DFM)-Analyse: Diese Technologie bietet eine umfassende DFM-Analyse, die Fertigung, Montage, Test, Flex/Starrflex, Substrat- und Panel-Validierung frühzeitig und zeitgleich zum Leiterplattendesign umfasst, ohne das Layout in der neuen Xpedition-Integrationsumgebung zu verlassen.

Sign-off der elektrischen Leistung: Durch die automatische Überprüfung der elektrischen Regeln (ERC) simultan zum Leiterplatten-Layout lassen sich kritische Signal-Integrität, Power-Integrität und EMI-/EMC-Probleme schnell identifizieren. Das soll die Dauer der Designüberprüfung von Tagen auf wenige Minuten beschleunigen.

Schneller Ergebnisse erreichen

„In Anbetracht der Tatsache, dass die Komplexität der Systemdesigns weiter zunimmt, ist eine der wichtigsten Initiativen von Mentor, unsere Kunden mit branchenführenden Verifizierungstechnologien zu unterstützen, die in der Vergangenheit in spezialisierten oder diskreten Instanzen eingesetzt wurden“, kommentierte A. J. Incorvaia, Senior Vice President von Mentor Electronic Board Systems. „Mit unserer neuen Xpedition-Plattform, die sich an Leiterplattendesigner richtet, ermöglichen diese integrierten Lösungen die Verifizierung innerhalb des Designprozesses. Auf diese Weise vereinfachen sie nicht nur die Bereitstellung, sondern verkürzen auch die Zeit bis zum Erreichen der Ergebnisse und helfen unseren Kunden, ihre Investitionen zu maximieren.“

Die Verifikationsplattform Xpedition ist verfügbar. Die Mentor-Tools unterstützen auch die meisten Designabläufe von Produkten anderer Hersteller.