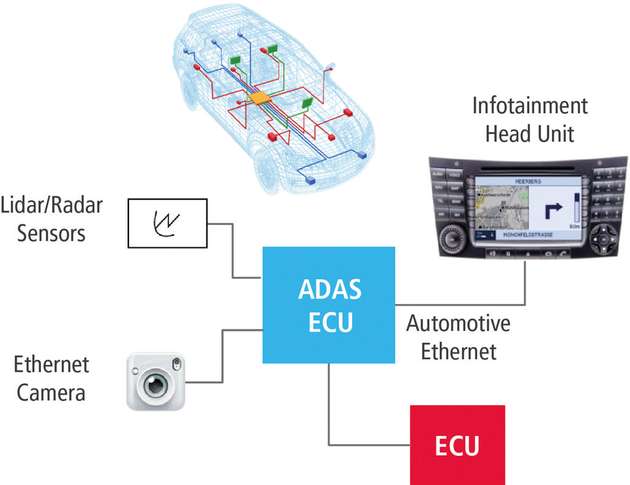

Von Advanced Driver Assist Systems (ADAS) über Kameras und Gateways bis hin zu Infotainment-Systemen – die Liste der Netzwerk-Anwendungen im Fahrzeug wird immer länger. Alle diese Komponenten erhöhen das Gewicht und die Komplexität eines Fahrzeugs. Um beides zu reduzieren, können die Entwickler alle diese Funktionen in ein einziges zusammenhängendes Steuergerät (ECU) integrieren. Diesen einzelnen Computer kann man als das Gehirn des Fahrzeugs und das Ethernet als dessen Nervenstränge betrachten. Die Ethernet-Spezifikation unterstützt unterschiedlichste Datenraten, die sich für Automobilanwendungen eignen. Von Megabits pro Sekunde bis Gigabits pro Sekunde – mit diesen Datenraten lassen sich viel robustere Netzwerk-Möglichkeiten im Fahrzeug realisieren. In der Industrie wird derzeit diskutiert, den Ethernet-Standard in Form eines Twisted-Pair-Kabels zu implementieren, was die Leitungsführung durch ein Fahrzeug auf kleinerem Raum erlauben würde. Bis jetzt ist das Automotive-Ethernet auf nichtkritische Systeme, wie Rückfahr- und Umgebungskameras beschränkt. Der BMW X5 nutzt ein einzelnes Twisted-Pair-Kabel mit 100-MBit/s-Ethernet als Verbindung für die Fahrerunterstützungskameras.

Die Open Alliance und die IEEE 802.3 Working Group arbeiten an der Entwicklung eines einheitlichen Fahrzeug-Ethernet-Standards. Der erste Entwurf dieses Standards wird noch in diesem Jahr erwartet. Damit können Anforderungen erweitert und Orientierungshilfen gegeben werden, durch die eine Verbreitung des Ethernets in anderen Automobilsystemen erleichtert wird. Eines Tages könnte man zum Beispiel das Ethernet nutzen, um das Navigationssystem mit der Getriebesteuerung zu verbinden, sodass der Fahrzeughersteller, die Getriebeübersetzung, je nach Art der Straßenbeschaffenheit, so verändern kann, dass eine maximale Kraftstoffeffizienz erzielt wird.

Vorteile der Verifikations-IP

Das Verständnis und die genaue Modellierung von Schnittstellen-Protokollen, welche die Datenraten definieren – mit Spezifikationen, die oft Hunderte oder sogar Tausende von Seiten lang sein können – ist eine schwierige und zeitraubende Aufgabe. Mit Verifikations-IP lassen sich System-on-Chip(SoC)-Designs schneller, gründlicher und mit weniger Aufwand verifizieren, so dass sich die Time-to-Market-Ziele bei Automobil-Designs einhalten lassen.

Wenn der Entwicklungsprozess einen Metric-Driven-Verifikationsansatz (MDV) nutzt, liefert das Ethernet-Verifikations-IP einen direkten Zugriff auf die Plan-basierte Methodik und damit einen Ethernet-spezifischen ausführbaren Verifikationsplan und eine Test Suite. Mittels Ethernet-Verifikations-IP kann man es vermeiden, Tausende von Einzeltests zu erstellen und diese zu warten.

Umfasst die Verifikations-IP zudem IP-Validierungstools, dann kann während der Logiksimulation noch vor der Fertigstellung des Halbleiters mit einem Stresstest das funktionale Verhalten mit einer eigenen Testbibliothek überprüft werden. Diese Fähigkeit automatisiert eine Verifikation der Protokoll-Konformität und verbessert damit die Effizienz und die Voraussagbarkeit.

Einige Verifikations-IPs unterstützen auch eine beschleunigte Verifikation. Dieser Ansatz ermöglicht einen Kompromiss zwischen Verifikationsfunktionalität und Simulationsgeschwindigkeit, im fortschreitenden Entwicklungsprozess vom Block- über Chip- bis hin zur Systemebene. Damit eignet sich dieser Ansatz für große Designs, wo eine Simulation mehrere Tage dauern kann. Dabei wird ein Emulator genutzt, um den Simulationstest der Verifikations-IP innerhalb weniger Minuten anstatt über mehrere Tage durchzuführen.

Auf Bauteilebene kann die Verifikations-IP sicherstellen, dass das Design diese Spezifikationen erfüllt:

IEEE 802.3 Standard für Ethernet PHY in Netzwerk-Anwendungen im Fahrzeug

Ethernet AVB (Audio Video Bridging) mit erweiterten Netzwerksfähigkeiten für eine Zeitsynchronisation (IEEE 802.1AS), Priority Queuing (IEEE 802.1p/802.1Q) und Traffic Shaping (IEEE 802.1Qav). Ethernet-AVB-Anwendungen umfassen On-Board-Diagnose, ADAS und Infotainment-Systeme.

Auf Systemebene kann die Verifikations-IP den Anwender bei der Entwicklung und Verifikation eines integrierten In-Vehicle-Ökosystems von Automotive Ethernet-konformen Technologien unterstützen. Der Einsatz von Verifikations-IP bietet folgende Möglichkeiten:

Modifikation von mehreren Ethernet-Frame-Formaten im selben Flow,

Fehlerinjektion in mehreren Sub-Layern und Nutzung verwandter Methoden, um Fehler zu verfolgen und zu identifizieren,

Steuerung der Übertragung von normalen Daten und Kontrollfeldern

Nutzung von Hilfsbibliotheken,

Nutzung von Verifikationsplänen, funktionaler Abdeckung und Test-Suites (mit Test-Abschnitten/Gruppen/Punkten und Familien, die Merkmalen und Bestimmungen aus der IEEE 802.3 Spezifikation entsprechen),

Steuerung und Synchronisation der Stimuli-Injektion bei mehreren Subsystemen gleichzeitig, um komplexe „reale“ Szenarien zu schaffen, die mehrere Endknoten und verschiedene Verkehrsmuster umfassen,

Modellierung und Testen von Ereignissen, Prioritäten und Leistung von sicherheitskritischen Systemen und

Nutzung von Scoreboard-Fähigkeiten mit Vorhersagemechanismen, in und außerhalb der Reihenfolge/Verluste, Suche, Kapselung und Transaktionsverfolgungs-Mechanismen.

Verifikations-IP für Kfz-Ethernet-Designs

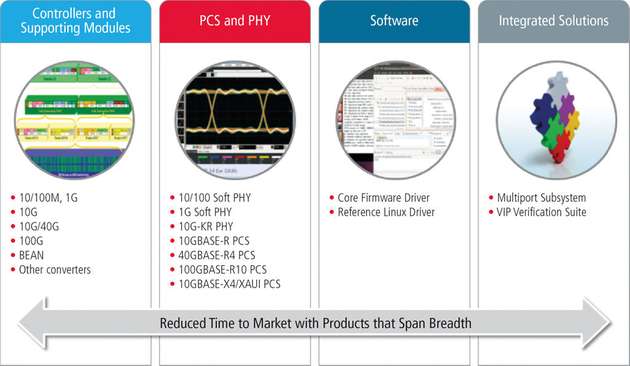

Cadence beteiligt sich an den Arbeitsgruppen für den IEEE 802.3-Standard und der Open Alliance, und stellt ein breites Portfolio von Verifikations-IP speziell für Automotive Ethernet-Designs zur Verfügung. Dieses Portfolio enthält Simulations-Verifikations-IP für Ethernet 25G/50G, Ethernet 40G/100G und Ethernet 10/100/1G/10G sowie beschleunigte Verifikations-IP für Ethernet 10/100/1G/10G und Ethernet 40G/100G.

Standardmäßig liefert die Verifikations-IP:

Modellierung aller in der Spezifikation beschriebenen Zustandsmaschinen,

Hunderte von Protokoll-Prüfungen, die den Regeln der Spezifikation entsprechen,

Unterstützung mehrerer Verifikationssprachen, einschließlich SystemVerilog und e,

optimierte Cores für eine dynamische Logiksimulation und Hardware-Beschleunigung sowie

Unterstützung aller gängigen Simulatoren sowie Cadence Incisive Formal Verifier und die Cadence-Palladium-XP-Verification-Computing-Plattform.

Zusätzlich zu Verifikations-IP bietet das Unternehmen auch Design-IP, wie ein AVB MAC Core und einen n-Port AVB Switch sowie Tensilica-HiFi Audio-, Sprach- und Sprech-DSPs (Digital Signal Processor) für Infotainment-Systeme und

Advanced Driver Assist Systems.