Zwanzig Jahre lang wurde das Wachstum von FPGAs durch den Ersatz von diskreten Logik-, ASIC- und ASSP-Bausteinen geschürt, die in Applikationen mit geringen oder mittleren Stückzahlen beispielsweise in den Marktbereichen Industrie, Medizin und Telekommunikations-Infrastruktur eingesetzt wurden. Beim Blick auf die kommenden zwanzig Jahre deuten zahlreiche Faktoren darauf hin, dass hochvolumige Geräte wie mobile Consumerprodukte zum Wachstumstreiber für FPGAs werden. Zu den entscheidenden Gründen für diese Entwicklung zählen die fortschreitenden Auswirkungen von Moore�??s Law sowie eine Innovations-Explosion im mobilen Verbraucherbereich.

Die mit FPGAs verbundenen Senkungen des Energiebedarfs und der Kosten veranschaulichen den Fortbestand von Moore´s Law auf drastische Weise. Im Jahre 1995 lagen die Kosten eines Bausteins, der mit einem FPGA von heute mit einer Kapazität von 256 LUT gleichzusetzen ist, bei mehr als 50 US-Dollar. Dieser wurde höchstwahrscheinlich in einem Fertigungsprozess mit 0,5 Mikron oder größer hergestellt: Wenig geeignet für ein Endverbrauchergerät, das im Einzelhandel für wenige Hundert US-Dollar verkauft wird. Heute setzen Bausteine mit dieser Kapazität einen 40-nm-Prozess ein und stehen für lediglich 0,50 US-Dollar zur Verfügung. Die Verbesserungen beim Leistungsverbrauch erweisen sich als gleichermaßen eindrucksvoll. Bei den im Beispiel genannten Bausteinen lag die typische statische Leistung bei 0,5 W. Diese wurde auf unter 50 µW reduziert. Mit diesem Preis- und Leistungsniveau sind FPGAs inzwischen zu einem technisch möglichen - und attraktiven - Baustein für eine hochvolumige Entwicklungslösung geworden. Darüber hinaus sind in Zukunft weitere Verbesserungen zu erwarten, die durch weitergehende Fortschritte der Technologie vorangetrieben werden. Angesichts der Tatsache, dass beim Übergang der Bauelemente von 40 auf 20 nm bis zu vierfache Einsparungen bei den Logikkosten zu erwarten sind, sowie im Zuge weiterer Verbesserungen beim Gesamtenergiebedarf erscheint ein zunehmender Einsatz von FPGAs in Geräten mit hohen Stückzahlen so gut wie sicher.

App-Stores, wie sie zum Beispiel für Android-Smartphones zur Verfügung stehen, sind Triebfedern für eine Hardware-Innovation. Vor fünf Jahren wurden die Anwendungen durch die Hardwarehersteller spezifiziert und gesteuert sowie durch die in einem Handy verfügbare Hardware eingeschränkt. Heutzutage leisten Hunderttausende von Applikationsentwicklern Beiträge für die Stores, die Software für mobile Geräte ausliefern. Viele dieser Entwickler erforschen neue Use Cases, welche die Hardwaremöglichkeiten bis an deren Grenzen ausloten und folglich die Geräteanbieter zwingen, neue Fähigkeiten vorzusehen. Der Schub zur Unterstützung der jeweils neuesten Apps zieht in Verbindung mit der ständig vorhandenen Notwendigkeit, eine Lösung von den anderen Lösungen im Markt zu differenzieren, eine Veränderung in der von Systementwicklern eingeschlagenen Lösungsmethode nach sich. Vor zehn Jahren konnten Systementwickler durch eine Kombination von ASICs und ASSPs zu neuen Fähigkeiten und Produktdifferenzierungen gelangen. Jedoch machen es die zunehmende Innovationsgeschwindigkeit und verkürzte Entwicklungszyklen immer schwieriger, teure und zeitraubende ASICs zu entwickeln und dabei die Zeitpläne einzuhalten. Deshalb wenden sich die Designer den ASSP-(Chipsatz-)Lösungen von einer immer kleineren Liste von Anbietern zu. Das freilich stellt die Entwickler vor neue Herausforderungen: Wenn alle dieselben Chipsätze verwenden, wie können sie dann ihre Produkte differenzieren?

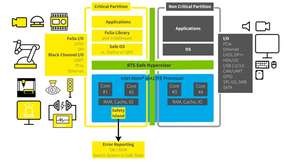

Infolge dieser Konvergenz von niedrigen Kosten und stromsparenden FPGAs, in Gang gehalten durch den unaufhaltsamen Siegeszug von Moore´s Law und unablässige Innovation, entsteht ein neues Modell für die Verwendung von FPGAs. Sie werden rasch in hochvolumigen Applikationen eingesetzt. Dort werden sie statt als Ersatz für vorhandene Bausteine als Ergänzung von ASSP-basierten Chipsätzen betrachtet. Das ermöglicht den Entwicklern das Erreichen einer schnelleren Time-to-Market bei niedrigen Kosten, geringem Stromverbrauch und mit der immer wichtiger werdenden Produktdifferenzierung.