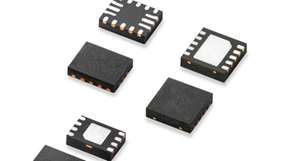

Eine neue Schnittstelle ist im Begriff, das Protokoll der Zukunft für Wandler zu werden. Die Schnittstelle JESD204 wurde erstmals 2006 vorgestellt. Sie bietet gegenüber ihren CMOS- und LVDS-Vorgängern Vorteile hinsichtlich Geschwindigkeit, Platzbedarf und Kosten. Schaltungen mit JESD204-Schnittstellen sind schneller und können mit den steigenden Abtastraten von Wandlern Schritt halten. Aufgrund der reduzierten Anzahl von Anschlüssen (Pins) ist der Einsatz kleinerer Gehäuse möglich. Außerdem sind beim JESD204-Standard weniger elektrische Verbindungen erforderlich. Ferner reduzieren sich mit dem JESD204-Standard die Kosten für das Gesamtsystem. Da der Standard von einer steigenden Zahl an Wandler-Herstellern und Anwendern akzeptiert wurde, hat man ihn weiter optimiert, um eine höhere Effizienz und eine einfache Implementierung zu ermöglichen. Der Standard eignet sich sowohl für A/D- wie auch für D/A-Wandler und gilt primär als einheitliche Schnittstelle für FPGAs - er kann aber auch in Verbindung mit ASICs verwendet werden.

Die ursprüngliche Version

Im April 2006 wurde die erste Version von JESD204 freigegeben. Der Standard beschreibt eine serielle Multi-Gigabit-Datenverbindung zwischen Wandlern und einem Empfänger. In dieser ursprünglichen Version von JESD204 wurde die serielle Datenverbindung für eine einzige serielle Leitung definiert. Die Verbindung ist die physikalische Schnittstelle zwischen einer Anzahl von „M“ Wandlern und dem Empfänger, der aus einem differenziellen Paar an Verbindungen besteht und CML-Treiber (Current Mode Logic) nutzt. Der Frame-Takt liegt an den Wandlern und den Empfängern an. Er stellt den Takt für die JESD204-Verbindung zwischen den Bauteilen zur Verfügung.Als Datenrate auf der Leitung (Lane) sind 312,5 MBit/s bis 3,125 GBit/s definiert. Quellen- und Lastimpedanz betragen dabei 100 �?� ±20 Prozent. Der Datenstrom wird in 8b/10b-Codierung mit einem eingebetteten Takt übertragen. Dies hat den Vorteil, dass kein zusätzliches Taktsignal übertragen werden muss, da das Taktsignal für den Decoder aus dem Datenstrom gewonnen wird. Beim praktischen Einsatz des JESD204-Standards hat sich gezeigt, dass der Standard überarbeitet werden musste, um Unterstützung für mehrere serielle Kanäle mit mehreren Wandlern zu erhalten. Nur so konnte er den zunehmenden Geschwindigkeiten und Auflösungen von Wandlern gerecht werden. Dies führte zur ersten Revision des JESD204-Standards im April 2008, JESD204A. Die Datenraten blieben unverändert. Die Revision ermöglichte es, mehrere ausgerichtete (aligned) serielle Leitungen zu unterstützen. Damit wurde es möglich, dass Wandler mit hohen Abtastraten und hohen Auflösungen die maximal unterstützte Datenrate von 3,125 GBit/s erreichen.

Deterministische Latenzen

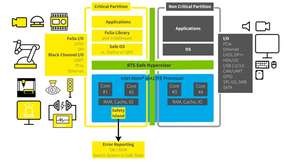

Obwohl JESD204 und JESD204A leistungsstärker als andere Schnittstellen sind, fehlte ihnen noch immer ein wichtiges Element: eine deterministische Latenz auf der Verbindung. Es ist wichtig, die Timing-Beziehung zwischen dem abgetasteten Signal und seiner digitalen Darstellung zu kennen, damit das abgetastete Signal sauber rekonstruiert werden kann, sobald das Signal empfangen wurde (eine ähnliche Situation gilt für einen D/A-Wandler). In den Versionen JESD204 und JESD204A des Schnittstellenstandards gab es keine definierten Fähigkeiten, welche die Latenz der seriellen, digitalen Ein-/Ausgangsdaten deterministisch setzen würden. Im Juli 2011 wurde die zweite und heute aktuelle Revision des Standards, JESD204B, veröffentlicht. Eine der wichtigen Komponenten des überarbeiteten Standards waren Erweiterungen zur Erzielung deterministischer Latenz. Ferner wurden die Datenraten bei Bauteilen mit verschiedenen Geschwindigkeitsstufen (Speed Grades) auf 12,5 GBit/s getrieben. Bei dieser Revision erfolgt ein Wechsel von der Nutzung des Frame-Takts zur Nutzung des Bausteintakts als Haupt-Taktquelle.

Baustein als Taktquelle

Das SYSREF-Signal dient als Master Timing-Referenz und richtet alle internen Teiler von Bausteintakten sowie die lokalen Multi-Frame Takte in jedem Transmitter und Empfänger aus. Dies hilft, deterministische Latenz im System sicherzustellen. Zusätzlich zur deterministischen Latenz erhöht die Version JESD204B die unterstützten Datenraten auf 12,5 GBit/s und teilt Bausteine in drei verschiedene Geschwindigkeitsstufen. Die erste Geschwindigkeitsstufe umfasst Datenraten bis 3,125 GBit/s, die zweite bis 6,375 GBit/s. Der zweite Speed Grade senkt den Ausgangsspannungspegel von 500 mVss der ersten Geschwindigkeitsstufe auf 400 mVss. Der dritte Speed Grade in der Revision JESD204B definiert die elektrische Schnittstelle für Datenraten bis 12,5 GBit/s. Diese Geschwindigkeitsstufe senkt den Ausgangsspannungspegel auf 360 mVss. Um eine höhere Flexibilität zu erzielen, geht die Revision JESD204B des Standards vom Frame-Takt zum Bausteintakt über. In den Revisionen JESD204 und JESD204A war der Frame-Takt die absolute Timing-Referenz im JESD204-System. Typischerweise waren der Frame-Takt und der Abtasttakt des oder der Wandler gleich. Dies bot keine hohe Flexibilität und konnte zu unerwünschter Komplexität im Systemdesign führen, wenn man versuchte, dieses gleiche Signal an mehrere Bausteine zu führen und einen Signalversatz (Skews) zwischen verschiedenen Routing-Pfaden zu verhindern. Jeder Wandler und Empfänger erhält seinen jeweiligen Bausteintakt von einem Taktgenerator. Dieser ist verantwortlich für die Erzeugung aller Bausteintakte von einer gemeinsamen Taktquelle.

JESD204 und seine Bedeutung

�?hnlich wie LVDS vor einigen Jahren begann, CMOS als Technologie zu überholen, befindet sich JESD204 heute auf einem vergleichbaren Weg. Mit steigender Datenrate auf CMOS-Ausgängen erhöhen sich auch die Ströme. Dies verursacht einen höheren Energieverbrauch. Während Strom- und Leistungsaufnahme bei LVDS relativ gleich bleiben, hat die Schnittstelle eine obere Geschwindigkeitsgrenze. Dies gilt für die Treiberarchitektur sowie für die vielen Datenleitungen, die auf einen Datentakt synchronisiert werden müssen. Bei etwa 150 bis 200 MSamples/s und 14 Bit Auflösung beginnen CML-Ausgangstreiber, hinsichtlich der Leistungsaufnahme effizienter zu werden. CML verlangt wegen der Serialisierung der Daten gegenüber LVDS und CMOS eine geringere Zahl an Ausgangspaaren für eine bestimmte Auflösung. Tabelle 1 zeigt die Anzahl der Pins bei einem 200 MSamples/s schnellen Wandler mit verschiedenen Kanalzahlen und Auflösungen. Bei den Werten werden ein Synchronisierungstakt für jeden Kanal für CMOS- und LVDS-Ausgänge sowie eine maximale Datenrate von 4 GBit/s für JESD204B mit den CML-Ausgängen angenommen. Wie die Tabelle zeigt, ist die Reduzierung der Pin-Anzahl mit der Revision JESD204B signifikant.

Standard der Zukunft

Mit steigender Geschwindigkeit und Auflösung von Wandlern hat sich der Bedarf an effizienteren Digitalschnittstellen erhöht. Die Branche realisierte dies mit der seriellen Datenschnittstelle JESD204. Der Standard hat sich weiterentwickelt und wurde mit der Zeit besser und schneller. Er wurde seit seinem Bestehen zwei Revisionen unterzogen, um seine Implementierung zu erleichtern und die steigende Nachfrage, hervorgerufen durch Wandler mit höheren Geschwindigkeiten und Auflösungen, zu erfüllen. Der Standard hat sich so entwickelt, dass er zu den vollzogenen �?nderungen und Optimierungen in der Wandler-Technologie passt. Ein Blick in die Zukunft zeigt, dass JESD204 dabei ist, zur Wahl der Branche als Digitalschnittstelle für Wandler zu werden. Während Systementwicklungen immer komplexer und die Leistungsfähigkeit von Wandlern immer weiter vorangetrieben werden, wird sich auch der JESD204-Standard anpassen, um auch künftig die erforderlichen Entwicklungsanforderungen zu erfüllen.